# Agilent N5393C PCI Express Automated Test Application

**Compliance Testing Methods of Implementation**

**Agilent Technologies**

# Notices

© Agilent Technologies, Inc. 2004-2010

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Manual Part Number**

Version 03.00.0000

#### **Edition**

Seventh edition, December 2010

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

## **Safety Notices**

## CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# PCI Express Automated Testing—At A Glance

The Agilent N5393C PCI Express Automated Test Application helps you verify PCI Express device under test (DUT) compliance to specifications with the Agilent 90000X Infinium digital storage oscilloscope. The PCI Express Automated Test Application:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- Creates a printable HTML report of the tests that have been run.

**NOTE** The tests performed by the PCI Express Automated Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

#### **Required Equipment and Software**

In order to run the PCI Express automated tests, you need the following equipment and software:

- N5393C PCI Express Automated Test Application software.

- 90000X series Infiniium Digital Storage Oscilloscope

- E2688A Serial Data Analysis and Clock Recovery software.

- Probes and/or test fixtures. For more information on the specific probes and test fixtures required, refer to the chapters that describe tests.

- N5380A Hi-BW differential SMA probe heads.

- Keyboard, qty = 1, (provided with the Agilent 90000X oscilloscope).

- Mouse, qty = 1, (provided with the Agilent 90000X oscilloscope).

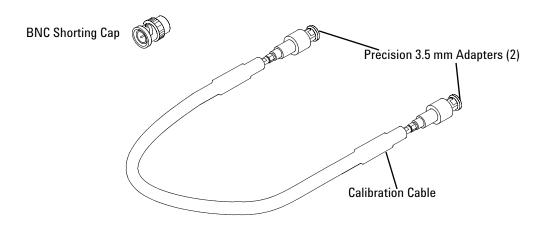

- Precision 3.5 mm BNC to SMA male adapter, qty = 2 (provided with the Agilent 90000X oscilloscope).

- 50-ohm Coax Cable with SMA Male Connectors 24-inch or less RG-316/U or similar, qty = 2, matched length.

# In This Book

This manual describes the tests that are performed by the PCI Express Automated Test Application in more detail; it contains information from (and refers to) the Base Specification, Card Electromechanical Specification, and ExpressCard Standard, and it describes how the tests are performed.

This manual is divided to several sections:

- Part I, "Introduction" covers the software and license installation and test preparation guide.

- Part II, "PCI Express Version 1.0a" covers the tests and Method of Implementation of PCI Express version 1.0a.

- Part III, "PCI Express Version 1.1" covers the tests and Method of Implementation of PCI Express version 1.1.

- Part IV, "2.5 GT/s PCI Express Version 2.0" covers the tests and Method of Implementation of 2.5 GT/s PCI Express version 2.0.

- Part V, "5.0 GT/s PCI Express Version 2.0" covers the tests and Method of Implementation of 5.0 GT/s PCI Express version 2.0.

- Part VI, "ExpressCard 1.0" covers the tests and Method of Implementation of ExpressCard version 1.0.

- Part VII, "PCI Express Version 3.0" covers the tests and Method of Implementation of PCI Express version 3.0.

- Part VIII, "Appendices" covers oscilloscope calibration, channel de-skew calibration and probe information.

The chapters in this book are:

- Chapter 1, "Installing the PCI Express Automated Test Application" shows how to install and license the automated test application software (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements" shows how to start the PCI Express Automated Test Application and gives a brief overview of how it is used.

- Chapter 3, "Transmitter (Tx) Tests, PCI-E 1.0a, Full Power" contains more information on the PCI Express version 1.0a transmitter tests.

- Chapter 4, "Transmitter (Tx) Tests, PCI-E 1.0a, Low Power" contains more information on the PCI Express version 1.0a transmitter tests.

- Chapter 5, "Receiver (Rx) Tests, PCI-E 1.0a" contains more information on the PCI Express version 1.0a receiver tests.

- Chapter 6, "Add-In Card (Tx) Tests, PCI-E 1.0a" contains more information on the PCI Express version 1.0a add-in card tests.

- Chapter 7, "System Board (Tx) Tests, PCI-E 1.0a" contains more information on the PCI Express version 1.0a system board tests.

- Chapter 8, "Reference Clock Tests, PCI-E 1.1" contains more information on the PCI Express version 1.1 reference clock tests.

- Chapter 9, "Transmitter (Tx) Tests, PCI-E 1.1, Full Power" contains more information on the PCI Express version 1.1 transmitter tests.

- Chapter 10, "Transmitter (Tx) Tests, PCI-E 1.1, Low Power" contains more information on the PCI Express version 1.1 transmitter tests.

- Chapter 11, "Receiver (Rx) Tests, PCI-E 1.1" contains more information on the PCI Express version 1.1 receiver tests.

- Chapter 12, "Add-In Card (Tx) Tests, PCI-E 1.1" contains more information on the PCI Express version 1.1 add-in card tests.

- Chapter 13, "System Board (Tx) Tests, PCI-E 1.1" contains more information on the PCI Express version 1.1 system board tests.

- Chapter 14, "Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 2.0, Full Power" contains more information on the PCI Express version 2.0, 2.5 GT/s transmitter tests.

- Chapter 15, "Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 2.0, Low Power" contains more information on the PCI Express version 2.0, 2.5 GT/s transmitter tests.

- Chapter 16, "Receiver (Rx) Tests, 2.5 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 2.5 GT/s receiver tests.

- Chapter 17, "Add-In Card (Tx) Tests, 2.5 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 2.5 GT/s add-in card tests.

- Chapter 18, "System Board (Tx) Tests, 2.5 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 2.5 GT/s system board tests.

- Chapter 19, "Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 5.0 GT/s transmitter tests.

- Chapter 20, "Receiver (Rx) Tests, 5.0 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 5.0 GT/s receiver tests.

- Chapter 21, "Add-In Card (Tx) Tests, 5.0 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 5.0 GT/s add-in card tests.

- Chapter 22, "System Board (Tx) Tests, 5.0 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 5.0 GT/s system board tests.

- Chapter 23, "Reference Clock Tests, 5.0 GT/s, PCI-E 2.0" contains more information on the PCI Express version 2.0, 5.0 GT/s reference clock tests.

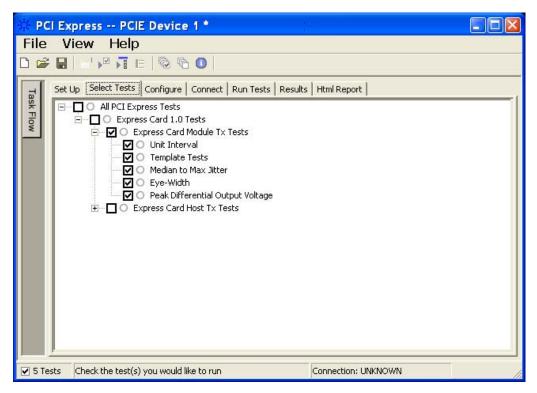

- Chapter 24, "ExpressCard Tests" contains more information on the ExpressCard version 1.0 module and host tests.

- Chapter 25, "Transmitter (Tx) Tests, PCI-E 3.0" contains more information on the PCI Express version 3.0 transmitter tests.

- Chapter 26, "Reference Clock Tests, PCI-E 3.0" contains more information on the PCI Express version 3.0 reference clock tests.

- Appendix A, "Calibrating the Digital Storage Oscilloscope" describes how to calibrate the oscilloscope in preparation for running the PCI Express automated tests.

- Appendix B, "InfiniiMax Probing Options" describes the probe amplifier and probe head recommendations for PCI Express testing.

- Appendix C, "INF\_SMA\_Deskew.set Setup File Details" describes a setup used when performing channel de-skew calibration.

- **See Also** The PCI Express Automated Test Application's online help, which describes:

- Starting the PCI Express Automated Test Application.

- Creating or opening a test project.

- Setting up the PCI Express test environment.

- Selecting tests.

- Configuring selected tests.

- Connecting the oscilloscope to the DUT.

- Running tests.

- Viewing test results.

- Viewing/printing the HTML test report.

- Saving test projects.

- Controlling the application via a remote PC.

# Contents

PCI Express Automated Testing—At A Glance 3 Required Equipment and Software 3 In This Book 4

## **Part I Introduction**

#### **1** Installing the PCI Express Automated Test Application

Installing the Software 21 Installing the License Key 21

#### **2** Preparing to Take Measurements

Calibrating the Oscilloscope 23

Starting the PCI Express Automated Test Application

24

Online Help Topics

25

Clock Recovery and Analysis (Applicable to PCI Express 1.0a Only) 27

## Part II PCI Express Version 1.0a

#### **3** Transmitter (Tx) Tests, PCI-E 1.0a, Full Power

Probing the Link for Tx Compliance32Single-Ended SMA Probing (Ch1) and (Ch3)33Single-Ended Probing (Ch1) and (Ch3)34Differential Probing (Ch2)35

Tx Compliance Test Load 36

Running Signal Quality Tests 36

Tx, Unit Interval 37

Tx, Template Tests 38

Tx, Median to Max Jitter 40

Tx, Eye-Width 41

Tx, Peak Differential Output Voltage 43

Tx, Rise/Fall Time 44

Tx, Deemphasized Voltage Ratio 46

Running Common Mode Voltage Tests 48

Tx, RMS AC Peak Common Mode Output Voltage 48

Tx, Avg DC Common Mode Output Voltage 50

Tx, DC Common Mode Line Delta 51

Tx, DC Common Mode Output Voltage Variation 52

#### 4 Transmitter (Tx) Tests, PCI-E 1.0a, Low Power

Probing the Link for Tx Compliance 57 **Tx Compliance Test Load** 57 **Running Signal Quality Tests** 57 Tx, Unit Interval 57 Tx, Template Tests (Low Power) 58 Tx, Median to Max Jitter (Low Power) 59 Tx, Eye-Width (Low Power) 59 Tx, Peak Differential Output Voltage (Low Power) 59 Tx, Rise/Fall Time 59

Running Common Mode Voltage Tests 60

## 5 Receiver (Rx) Tests, PCI-E 1.0a

Probing the Link for Rx Compliance 62 Single-Ended Probing (Ch1) and (Ch3) 63 Differential Probing (Ch2) 64 **Running Receiver Tests** 65 Unit Interval 65 **Template Test** 66 Median to Max Jitter 67 68 Eye-Width

Peak Differential Output Voltage70AC Peak Common Mode Input Voltage71

# 6 Add-In Card (Tx) Tests, PCI-E 1.0a

Probing the Link for Add-In Card Compliance 74 Connecting the Signal Quality Load Board for Add-in Card Testing 74 **Running Add-In Card Tests** 77 Unit Interval 77 **Template Tests** 78 Median to Max Jitter 79 Eve-Width 81 Peak Differential Output Voltage 82

## 7 System Board (Tx) Tests, PCI-E 1.0a

Probing the Link for System Board Compliance 85 Connecting the Signal Quality Load Board for System/Motherboard Testing 85

**Running System Board Tests** 87 Unit Interval 88 **Template Tests** 89 Median to Max Jitter 90 Eye-Width 92 Peak Differential Output Voltage 93

## Part III PCI Express Version 1.1

#### 8 Reference Clock Tests, PCI-E 1.1

Probing the Link for Reference Clock Compliance 98 Single-Ended SMA Probing 99 Single-Ended Probing 100 **Differential Probing** 101

**Reference Clock Measurement Point** 102

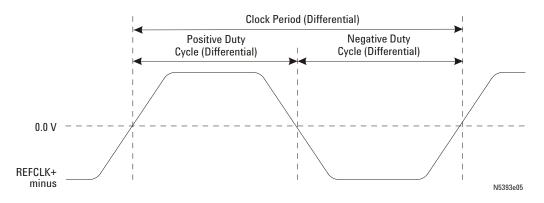

**Running Reference Clock Tests** 102 Phase Jitter 103 **Rising Edge Rate** 105 107 Falling Edge Rate **Differential Input High Voltage** 108 **Differential Input Low Voltage** 109 Average Clock Period 110 Duty Cycle 112

## 9 Transmitter (Tx) Tests, PCI-E 1.1, Full Power

Probing the Link for Tx Compliance 114 Single-Ended SMA Probing 115 Single-Ended Probing 116 **Differential Probing** 117 **Tx Compliance Test Load**

118

**Running Signal Quality Tests** 118 Unit Interval 120 **Template Tests** 121 Median to Max Jitter 123 Eye-Width 125 Peak Differential Output Voltage 127 Rise/Fall Time 128 **De-emphasized Voltage Ratio** 130 **Running Common Mode Voltage Tests** 131 RMS AC Peak Common Mode Output Voltage 132 Avg DC Common Mode Output Voltage 134 DC Common Mode Line Delta 136 DC Common Mode Output Voltage Variation 137

#### 10 Transmitter (Tx) Tests, PCI-E 1.1, Low Power

Probing the Link for Tx Compliance 141 **Tx Compliance Test Load** 141 **Running Signal Quality Tests** 141 Unit Interval 141 Template Tests (Low Power) 142 Median to Max Jitter (Low Power) 143 Eye-Width (Low Power) 143 Peak Differential Output Voltage (Low Power) 143 Rise/Fall Time 143

Running Common Mode Voltage Tests 144

## 11 Receiver (Rx) Tests, PCI-E 1.1

Probing the Link for Rx Compliance 146 Single-Ended Probing 146 **Differential Probing** 147 **Running Receiver Tests** 149 Unit Interval 149 **Template Test** 150 Median to Max Jitter 151 Eye-Width 152 Peak Differential Output Voltage 154 AC Peak Common Mode Input Voltage 155

#### 12 Add-In Card (Tx) Tests, PCI-E 1.1

Probing the Link for Add-In Card Compliance 158

Connecting the Signal Quality Load Board for Add-in Card Testing 158

Running Add-In Card Tests 161

Unit Interval 162 Template Tests 164 Median to Max Jitter 166 Eye-Width 167 Peak Differential Output Voltage 169

# 13 System Board (Tx) Tests, PCI-E 1.1

Probing the Link for System Board Compliance 172 Connecting the Signal Quality Load Board for System/Motherboard Testing 172

Running System Board Tests 174 Unit Interval 175 Template Tests 176 Median to Max Jitter 178 Eye-Width 179

Peak Differential Output Voltage 180

# Part IV 2.5 GT/s PCI Express Version 2.0

## 14 Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 2.0, Full Power

Probing the Link for Tx Compliance 186 Single-Ended SMA Probing 187 Single-Ended Probing 188 **Differential Probing** 189 Tx Compliance Test Load 190 **Running Signal Quality Tests** 190 Tx, Unit Interval 192 Tx, Template Tests 193 Tx, Median to Max Jitter 194 Tx, Eye-Width 196 Tx, Peak Differential Output Voltage 198 Tx, Rise/Fall Time 199 Tx, De-emphasized Voltage Ratio 201

Running Common Mode Voltage Tests 203 Tx, RMS AC Peak Common Mode Output Voltage Tx, Avg DC Common Mode Output Voltage 205 Tx, DC Common Mode Line Delta 206 Tx, DC Common Mode Output Voltage Variation

204

207

# 15 Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 2.0, Low Power

Probing the Link for Tx Compliance 211 Tx Compliance Test Load 211 **Running Signal Quality Tests** 211 Tx, Unit Interval 211 Tx, Template Tests (Low Power) 212 Tx, Median to Max Jitter (Low Power) 212 Tx, Eye-Width (Low Power) 212 Tx, Peak Differential Output Voltage (Low Power) 213 Tx, Rise/Fall Time 213

Running Common Mode Voltage Tests 214

## 16 Receiver (Rx) Tests, 2.5 GT/s, PCI-E 2.0

Probing the Link for Rx Compliance 216 Single-Ended Probing 216 **Differential Probing** 217 **Running Receiver Tests** 219 Rx, Unit Interval 219 Rx, Template Test 220 Rx, Median to Max Jitter 221 Rx, Eye-Width 222 Rx, Peak Differential Output Voltage 224 Rx, AC Peak Common Mode Input Voltage 225

## 17 Add-In Card (Tx) Tests, 2.5 GT/s, PCI-E 2.0

Probing the Link for Add-In Card Compliance 228 Connecting the Signal Quality Load Board for Add-in Card Testing 228 **Running Add-In Card Tests** 231 Add-In Card Tx, Unit Interval 232 Add-In Card Tx, Template Tests 233 Add-In Card Tx, Median to Max Jitter 234 Add-In Card Tx, Eye-Width 235 Add-In Card Tx, Peak Differential Output Voltage 236

#### 18 System Board (Tx) Tests, 2.5 GT/s, PCI-E 2.0

Probing the Link for System Board Compliance 240

Connecting the Signal Quality Load Board for System/Motherboard Testing 240

Running System Board Tests 242

System Board Tx, Unit Interval243System Board Tx, Template Tests244Median to Max Jitter246Eye-Width247

## Part V 5.0 GT/s PCI Express Version 2.0

## 19 Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 2.0

Probing the Link for Tx Compliance 254 Single-Ended SMA Probing (Ch1) and (Ch3) 255 Single-Ended Probing (Ch1) and (Ch3) 256 Differential Probing (Ch2) 257 **Tx Compliance Test Load** 258 **Running Tx Tests** 258 Tx, Unit Interval 259 Tx, Rise/Fall Time 261 Tx, De-emphasized Voltage Ratio 265 Tx, Average DC Common Mode Output Voltage 267 Tx, DC Common Mode Line Delta 269 Tx, Deterministic Jitter > 1.5 MHz 270 Tx, RMS Jitter < 1.5 MHz 273 Tx, Template Tests 275 Tx, Eye Width 277 Tx, Peak Differential Output Voltage 279

## 20 Receiver (Rx) Tests, 5.0 GT/s, PCI-E 2.0

Probing the Link for Rx Compliance284Single-Ended Probing (Ch1) and (Ch3)285Differential Probing (Ch2)286

Running Receiver Tests 287 Rx, Unit Interval (Data Clocked, Common Refclk) 287 Rx, Template Test 289 Rx, Peak Differential Output Voltage 291 Rx, RMS Random Jitter 293 Rx, Maximum Deterministic Jitter 296 Rx, Total Jitter at BER-12 298

## 21 Add-In Card (Tx) Tests, 5.0 GT/s, PCI-E 2.0

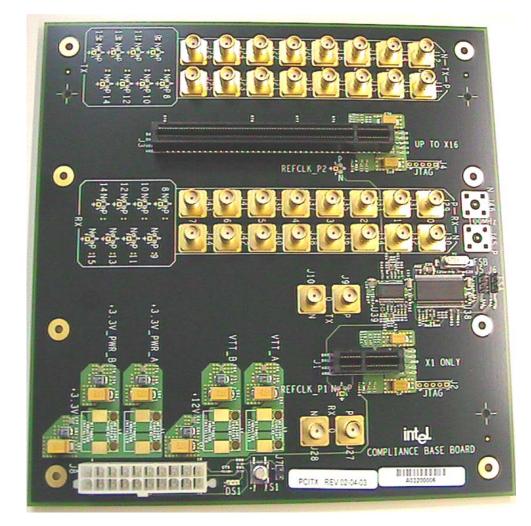

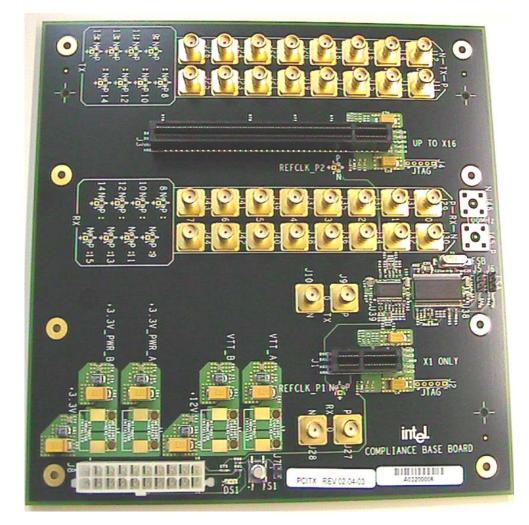

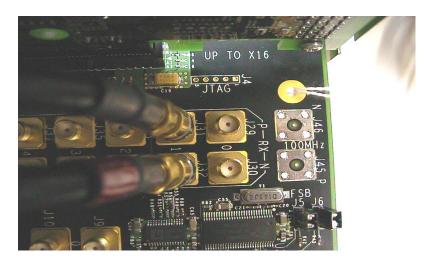

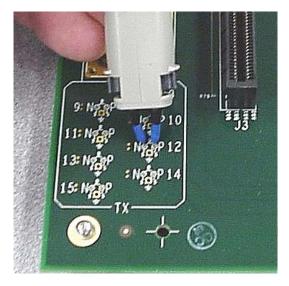

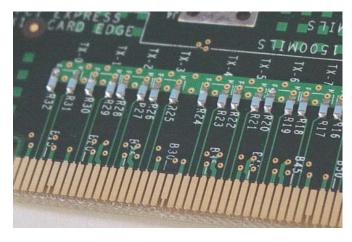

Probing the Link for Add-In Card Compliance 302 Connecting the Compliance Base Board for Add-in Card Testing 302 **Running Add-In Card Tests** 305 Add-In Card Tx, Unit Interval 305 Add-In Card Tx, Template Tests 307 Add-In Card Tx, Peak Differential Output Voltage 310 Add-In Card Tx, Eye-Width 313 Add-In Card Tx, RMS Random Jitter 316 Add-In Card Tx, Maximum Deterministic Jitter 318 Add-In Card Tx, Total Jitter at BER-12 320

# 22 System Board (Tx) Tests, 5.0 GT/s, PCI-E 2.0

Probing the Link for System Board Compliance 323 Connecting the Signal Quality Load Board for System/Motherboard Testing 323 **Running System Board Tests** 325 System Board Tx, Unit Interval 325 System Board Tx, Template Tests 327 System Board Tx, Peak Differential Output Voltage 330 System Board Tx, Eye-Width 333 System Board Tx, RMS Random Jitter 335 System Board Tx, Maximum Deterministic Jitter 338 System Board Tx, Total Jitter at BER-12 340

## 23 Reference Clock Tests, 5.0 GT/s, PCI-E 2.0

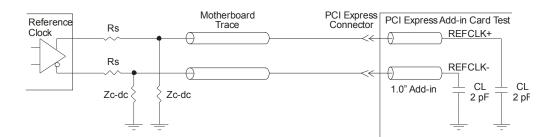

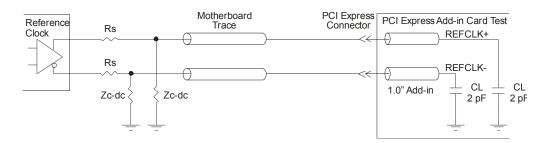

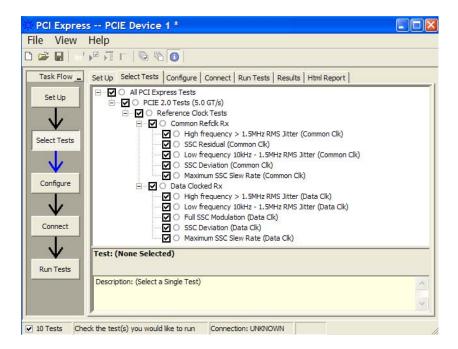

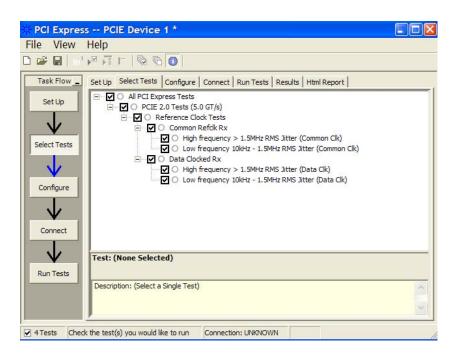

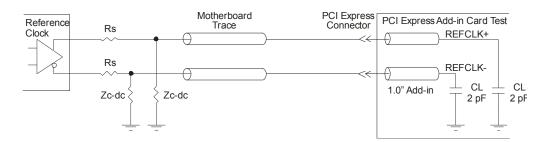

Reference Clock Architectures344Common Clock Architecture344Data Clock Architecture345

Probing the Link for Reference Clock Compliance 346 Single-Ended SMA Probing 348 Single-Ended Probing 349 **Differential Probing** 350 **Reference Clock Measurement Point** 351 **Running Reference Clock Tests** 351 Reference Clock, High Frequency >1.5 MHz RMS Jitter (Common Clk) 352 Reference Clock, SSC Residual (Common Clk) 354 Reference Clock, Low Frequency 10 kHz to 1.5 MHz RMS Jitter (Common Clk) 355 Reference Clock, SSC Deviation (Common Clk) 357 Reference Clock, Maximum SSC Slew Rate (Common Clk) 358 Reference Clock, High Frequency >1.5 MHz RMS Jitter (Data Clk) 359 Reference Clock, Full SSC Modulation (Data Clk) 360 Reference Clock, Low Frequency 10 kHz to 1.5 MHz RMS Jitter (Data Clk) 362 Reference Clock, SSC Deviation (Data Clk) 363 Reference Clock, Maximum SSC Slew Rate (Data Clk) 364

# Part VI ExpressCard 1.0

#### 24 ExpressCard Tests

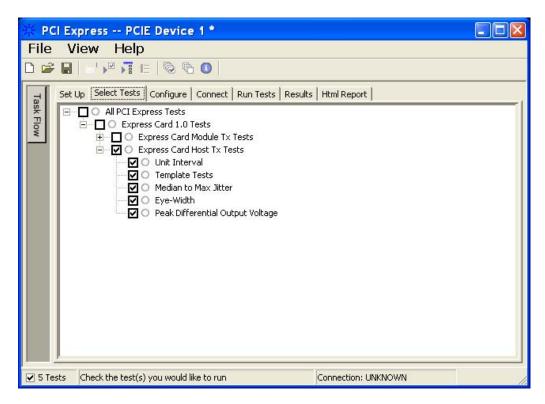

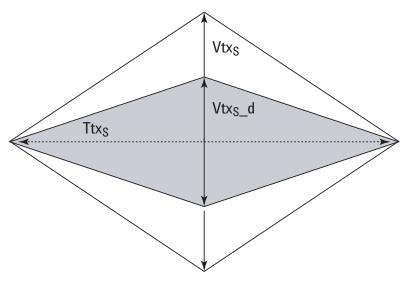

ExpressCard Module Tx Tests 369 Probing the Link for ExpressCard Module Compliance 369 Running ExpressCard Module Tx Tests 369 ExpressCard Module Tx, Unit Interval 370 ExpressCard Module Tx, Template Tests 371 ExpressCard Module Tx, Median to Max Jitter 373 ExpressCard Module Tx, Eye-Width 374 ExpressCard Module Tx, Peak Differential Output Voltage 376 ExpressCard Host Tx Tests 377 Probing the Link for ExpressCard Host Compliance 377 Running ExpressCard Host Tx Tests 377 ExpressCard Host Tx, Unit Interval 378 ExpressCard Host Tx, Template Tests 379 ExpressCard Host Tx, Median to Max Jitter 381 ExpressCard Host Tx, Eye-Width 382 ExpressCard Host Tx, Peak Differential Output Voltage 384

### Part VII PCI Express Version 3.0

### 25 Transmitter (Tx) Tests, PCI-E 3.0

Probing the Link for Tx Compliance 390 Single-Ended SMA Probing (Ch1) and (Ch3) 391 Single-Ended Probing (Ch1) and (Ch3) 392 **Differential Probing (Ch2)** 393 **Tx Compliance Test Load** 394 Running Tx Tests 394 395 Tx, Unit Interval Tx, Full Swing Tx Voltage with no TxEQ 397 Tx, Reduced Swing Tx Voltage with no TxEQ 399 Tx, Min Swing During EIEOS for Full Swing 401 404 Tx, Min Swing During EIEOS for Reduced Swing Tx, Uncorrelated Total Jitter 406 Tx, Uncorrelated Deterministic Jitter 408 Tx, Total Uncorrelated PWJ (Pulse Width Jitter) 409 Tx, Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) 411 Tx, Data Dependent Jitter 412 Tx, Pseudo Package Loss 414 Tx, DC Common-Mode Voltage 416 Tx, AC Common-Mode Voltage (4 GHz LPF) 417 Tx, AC Common-Mode Voltage (30 kHz to 500 MHz) 419 Tx, Absolute Delta of DC Common-Mode Voltage Between D+ and D-420 Tx, Absolute Delta of DC Common-Mode Voltage During L0 and Idle 421 Tx, Preset #1 Measurement (P1), De-emphasis 422 Tx, Preset #0 Measurement (P0), De-emphasis 425 Tx, Preset #9 Measurement (P9), Preshoot 427 429 Tx, Preset #8 Measurement (P8), De-emphasis Tx, Preset #8 Measurement (P8), Preshoot 432 Tx, Preset #7 Measurement (P7), De-emphasis 434 Tx, Preset #7 Measurement (P7), Preshoot 436 Tx, Preset #5 Measurement (P5), Preshoot 438 Tx, Preset #6 Measurement (P6), Preshoot 440 Tx, Preset #3 Measurement (P3), De-emphasis 442 Tx, Preset #2 Measurement (P2), De-emphasis 445 Tx, Preset #10 Measurement (P10), De-emphasis 447

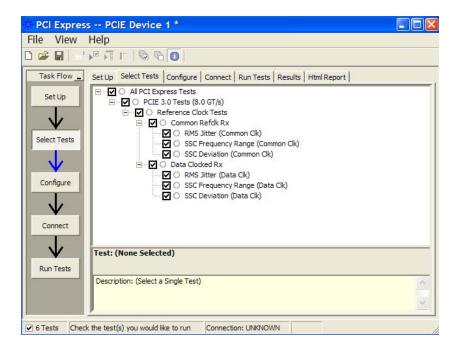

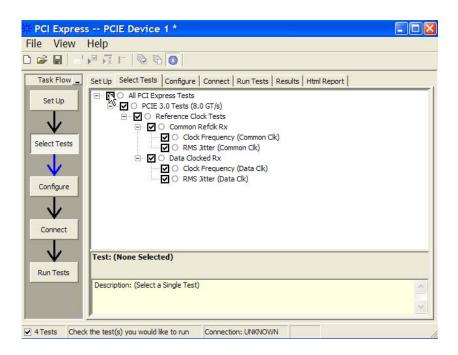

## 26 Reference Clock Tests, PCI-E 3.0

**Reference Clock Architectures** 452 **Common Clock Architecture** 452 Data Clock Architecture 453 Probing the Link for Reference Clock Compliance 453 Single-Ended SMA Probing 455 Single-Ended Probing 456 **Differential Probing** 457 **Reference Clock Measurement Point** 458 **Running Reference Clock Tests** 458 Reference Clock, Clock Frequency (Common Clk) 459 Reference Clock, RMS Jitter (Common Clk) 460 Reference Clock, SSC Frequency Range (Common Clk) 461 Reference Clock, SSC Deviation (Common Clk) 462 Reference Clock, Clock Frequency (Data Clk) 463 Reference Clock, RMS Jitter (Data Clk) 464 Reference Clock, SSC Frequency Range (Data Clk) 465 Reference Clock, SSC Deviation (Data Clk) 466

# **Part VIII Appendices**

#### A Calibrating the Digital Storage Oscilloscope

Required Equipment for Calibration470Internal Calibration471Cable and Probe Calibration477Channel-to-Channel De-skew486

- **B** InfiniiMax Probing Options

- C INF\_SMA\_Deskew.set Setup File Details

Index

# Part I Introduction

# Part I

Agilent N5393C PCI Express Automated Test Application Compliance Testing Methods of Implementation

# Installing the PCI Express Automated Test Application

Installing the Software 21 Installing the License Key 21

If you purchased the N5393C PCI Express Automated Test Application separately, you need to install the software and license key.

# Installing the Software

- 1 To obtain the PCI Express Automated Test Application, go to Agilent website: <u>http://www.agilent.com/find/N5393C</u>

- **2** The link for PCI Express Automated Test Application will appear. Double-click on it and follow the instructions to download and install the application software.

Be sure to accept the installation of the .NET Framework software; it is required in order to run the PCI Express Automated Test Application.

# **Installing the License Key**

1 Request a license code from Agilent by following the instructions on the Entitlement Certificate.

You will need the oscillocope's "Option ID Number", which you can find in the **Help>About Infinium...** dialog.

- 2 After you receive your license code from Agilent, choose Utilities>Install Option License....

- **3** In the Install Option License dialog, enter your license code and click **Install License**.

- **4** Click **OK** in the dialog that tells you to restart the Infiniium oscilloscope application software to complete the license installation.

- 5 Click Close to close the Install Option License dialog.

- 6 Choose File>Exit.

- **7** Restart the Infiniium oscilloscope application software to complete the license installation.

# 1 Installing the PCI Express Automated Test Application

2

Agilent N5393C PCI Express Automated Test Application Compliance Testing Methods of Implementation

# **Preparing to Take Measurements**

Calibrating the Oscilloscope 23 Starting the PCI Express Automated Test Application 24 Clock Recovery and Analysis (Applicable to PCI Express 1.0a Only) 27

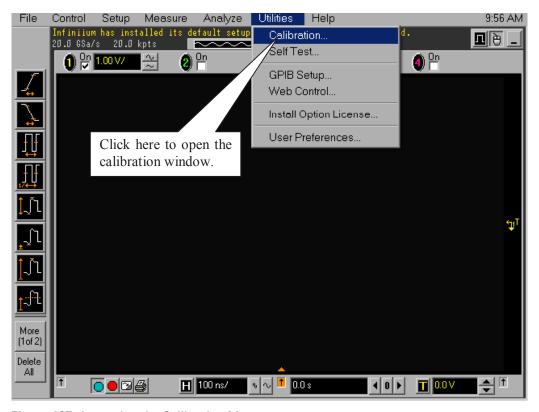

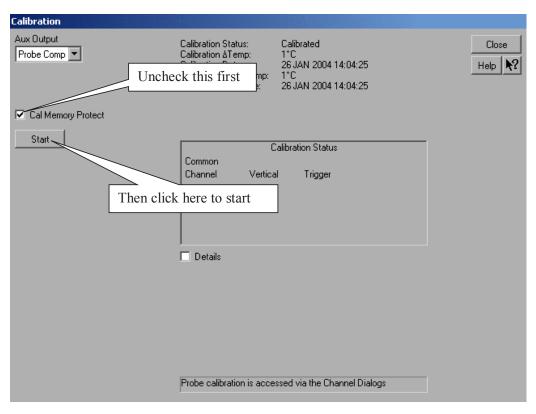

Before running the PCI Express automated tests, you should calibrate the oscilloscope. After the oscilloscope has been calibrated, you are ready to start the PCI Express Automated Test Application and perform measurements.

# **Calibrating the Oscilloscope**

If you haven't already calibrated the oscilloscope, see Appendix A, "Calibrating the Digital Storage Oscilloscope".

NOTE

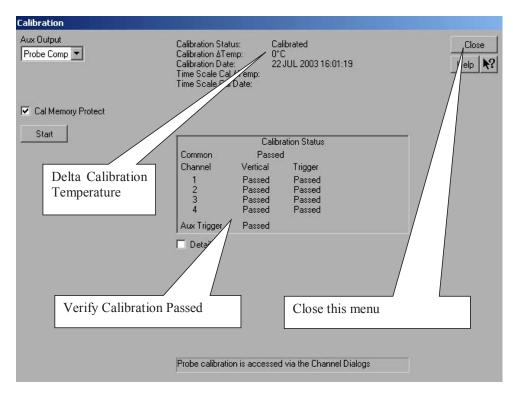

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the Utilities>Calibration menu.

**NOTE** If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration and channel de-skew calibration again. Agilent recommends that, once calibration is performed, you label the cables with the channel they were calibrated for.

## **2** Preparing to Take Measurements

# **Starting the PCI Express Automated Test Application**

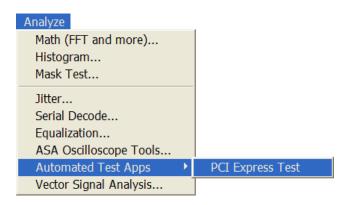

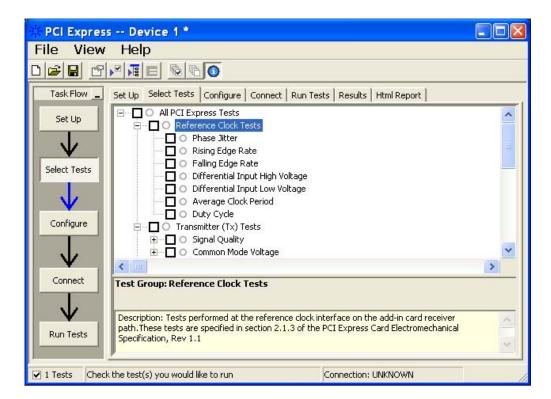

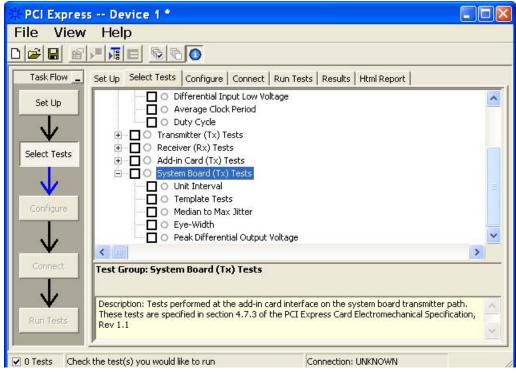

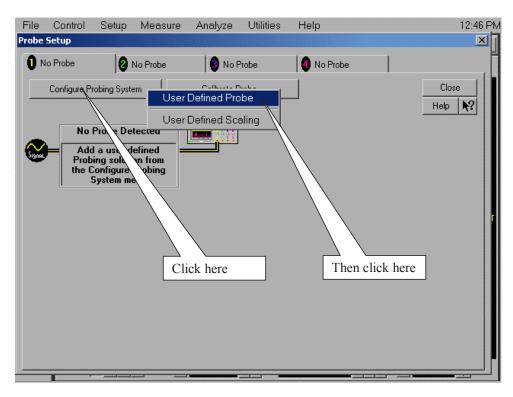

1 From the Infiniium oscilloscope's main menu, choose Analyze>Automated Test Apps>PCI Express.

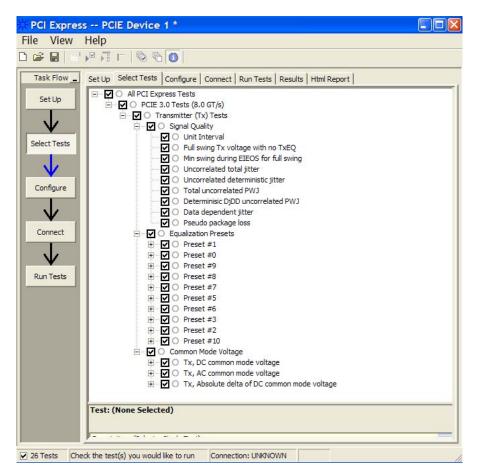

| sk Flow Set Up Select Te                                                                                                            | sts   Configure   Connect   Run Tests   Results | Html Report                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Set Up<br>Set Up<br>C PCIE 1.0a<br>C PCIE 1.0a<br>C PCIE 1.0a<br>C PCIE 2.0<br>C Express Ca<br>C PCIE 3.0<br>Device 1D:<br>Device 1 | ard 1.0                                         | Test Information<br>Reference Clock<br>☐ SSC<br>☑ Clean Clock<br>De-Emphasis Mode<br>ⓒ -3.5 dB<br>ⓒ -6.0 dB<br>Power Level<br>ⓒ Full |

| onnect                                                                                                                              | Use saved waveform                              | C Half<br>Data Rate<br>C 2.5 GT/s<br>© 5.0 GT/s                                                                                      |

| Test Report<br>User Comments                                                                                                        |                                                 |                                                                                                                                      |

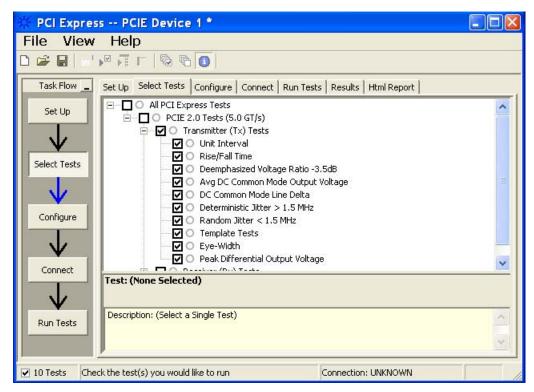

Figure 1 The PCI Express Automated Test Application

NOTE

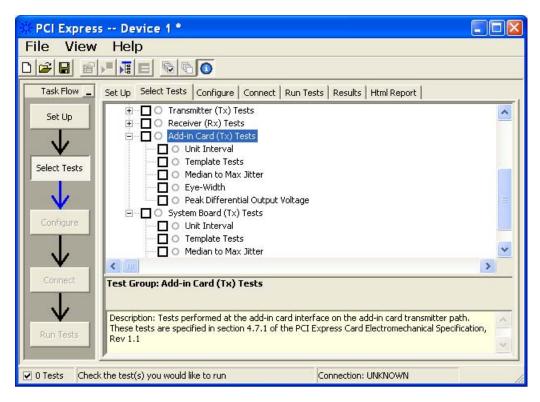

If PCI Express does not appear in the Automated Test Apps menu, the PCI Express Automated Test Application has not been installed (see Chapter 1, "Installing the PCI Express Automated Test Application"). Figure 1 shows the PCI Express Automated Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Set Up       | Lets you identify and set up the test environment,<br>including information about the device under test.                                                                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select Tests | Lets you select the tests you want to run. The tests are<br>organized hierarchically so you can select all tests in a<br>group. After tests are run, status indicators show which<br>tests have passed, failed, or not been run, and there are<br>indicators for the test groups. |

| Configure    | Lets you configure the test parameters (like memory depth). This information appears in the HTML report.                                                                                                                                                                          |

| Connect      | Shows you how to connect the oscilloscope to the device<br>under test for the tests to be run.                                                                                                                                                                                    |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing.        |

| Results      | Contains more detailed information about the tests that<br>have been run. You can change the thresholds at which<br>marginal or critical warnings appear.                                                                                                                         |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                               |

# **Online Help Topics**

For information on using the PCI Express Automated Test Application, see its online help (which you can access by choosing Help>Contents... from the application's main menu).

The PCI Express Automated Test Application's online help describes:

- Starting the PCI Express Automated Test Application.

- To view or minimize the task flow pane.

- To view or hide the toolbar.

- Creating or opening a test project.

- Setting up the test environment.

- To set up InfiniiSim.

- To load saved waveforms.

- Selecting tests.

#### **2** Preparing to Take Measurements

- Configuring selected tests.

- Connecting the oscilloscope to the Device Under Test (DUT).

- Running tests.

- To select the "store mode".

- To run multiple times.

- To send email on pauses or stops.

- To specify the event.

- To set the display preferences.

- To set the run preferences.

- Viewing test results.

- To delete trials from the results.

- To show reference images and flash mask hits.

- To change margin thresholds.

- To change the test display order.

- To set trial display preferences.

- Viewing/exporting/printing the HTML test report.

- To export the report.

- To print the report.

- Saving test projects.

- To set AutoRecovery preferences.

- Controlling the application via a remote PC.

- To check for the App Remote license.

- To identify the remote interface version.

- To enable the remote interface.

- To enable remote interface hints.

- Using a second monitor.

# **Clock Recovery and Analysis (Applicable to PCI Express 1.0a Only)**

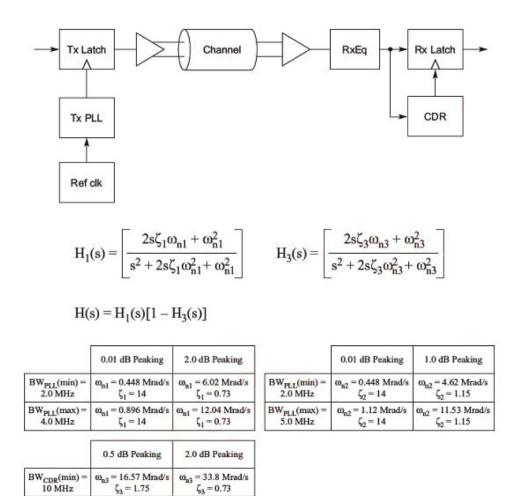

As described in Section 4.3.3.1 of the Base Specification, the following methodology is used to define the data set for all PCI Express eye and jitter measurements.

- The clock recovery window is 3500 consecutive Unit Intervals and the Mean of the UIs is used as the reference clock. The first 3500 UIs in the acquisition are used.

- An analysis window is established to be 250 bits centered in the 3500 UI clock recovery window. The mask is placed based on the median of the 250 bit analysis window.

- If there are enough data points in the record, the clock recovery window is advanced by 100 UI, a new mean UI is computed, and analysis is repeated over the middle 250 UI. This process is repeated until the advancing clock recovery window passes the end of the data record.

# 2 Preparing to Take Measurements

# Part II PCI Express Version 1.0a

# Part II

Agilent N5393C PCI Express Automated Test Application Compliance Testing Methods of Implementation

# Transmitter (Tx) Tests, PCI-E 1.0a, Full Power

Probing the Link for Tx Compliance 32 Tx Compliance Test Load 36 Running Signal Quality Tests 36 Running Common Mode Voltage Tests 48

This section provides the Methods of Implementation (MOIs) for Transmitter tests using an Agilent 90000X series Infinium oscilloscope, 1134A or 1169A probes, and the PCI Express Automated Test Application.

**3** Transmitter (Tx) Tests, PCI-E 1.0a, Full Power

# **Probing the Link for Tx Compliance**

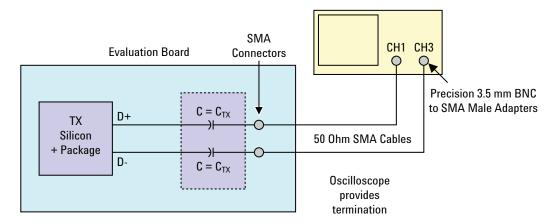

Transmitter tests are done by connecting the device under test to a test fixture and probing the SMA connectors on the test fixture. To probe the transmitter link, you can:

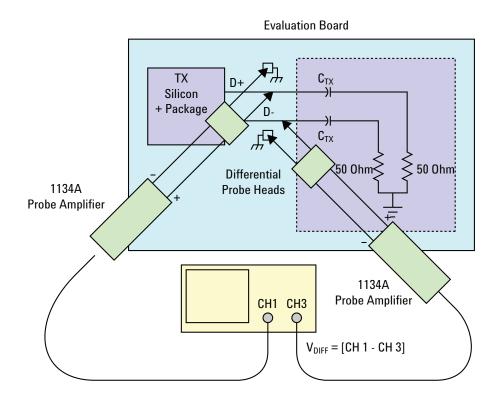

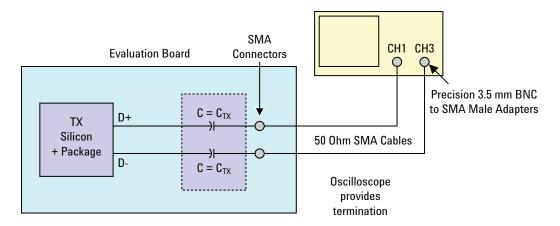

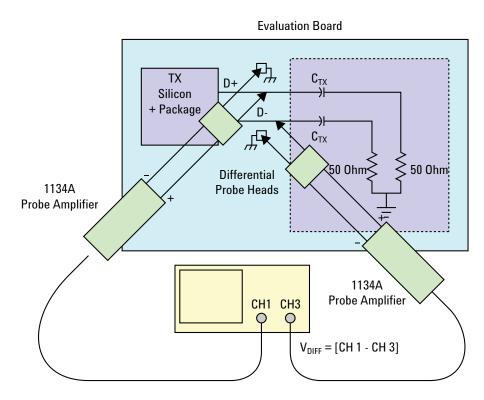

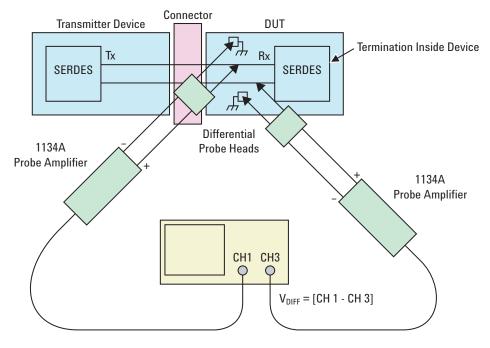

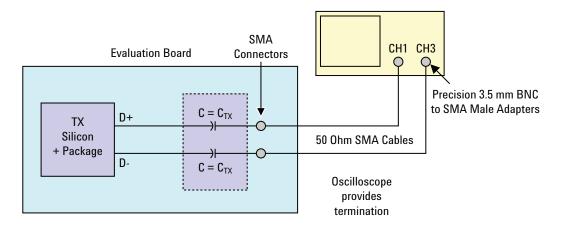

- Use two 50-ohm coax cables with SMA male connectors, two precision 3.5 mm BNC to SMA male adapters (included with the oscilloscope), and the Ch1 and Ch3 inputs of an oscilloscope that has 20 GS/s sample rate available on two channels.

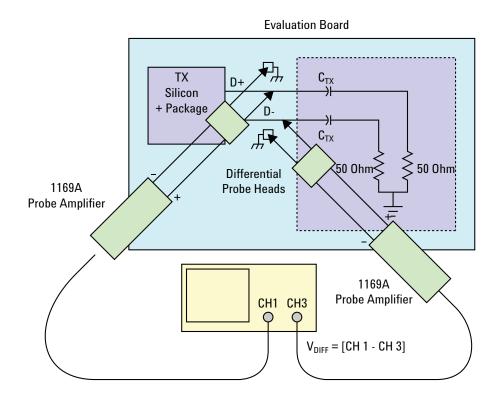

- Use two differential probe heads with two 1134A probe amplifiers (with the negative lead grounded for single-ended measurements) and the Ch1 and Ch3 inputs of an oscilloscope that has 20 GS/s sample rate available on two channels.

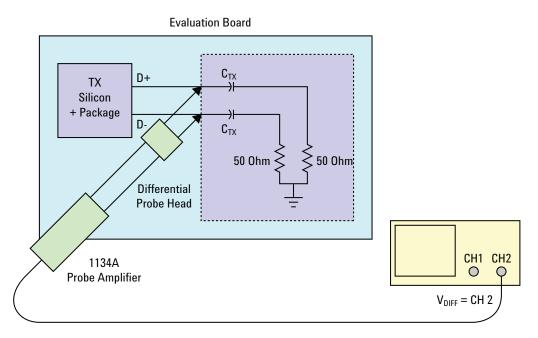

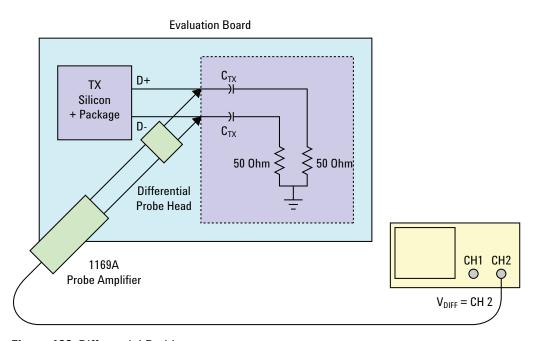

- Use one differential probe head with the 1134A probe amplifier and the Ch2 input of an oscilloscope that has 20 GS/s sample rate available on that channel.

When the link is broken and terminated into a 50 ohm load (by the test load), the Compliance Pattern defined in section 4.2.8 (Base Specification) will be transmitted.

|                   | Probing Configurations                                        |                         |                  | Captured Waveforms   |                |

|-------------------|---------------------------------------------------------------|-------------------------|------------------|----------------------|----------------|

|                   | Probing Method                                                | Break<br>Serial<br>Link | Channels<br>Used | Differential<br>Mode | Common<br>Mode |

| DUT<br>Connection | Single-Ended SMA<br>(2 x 50-Ohm SMA<br>Cables)                | Y                       | 2                | Pseudo               | Yes            |

|                   | Single-Ended<br>(2 x 1134A w/<br>Differential Probe<br>Heads) | Y/N                     | 2                | Pseudo               | Yes            |

|                   | Differential<br>(1 x 1134A w/<br>Differential Probe<br>Head)  | Y/N                     | 1                | True                 | No             |

#### **Table 1** Probing Options for Transmitter Testing

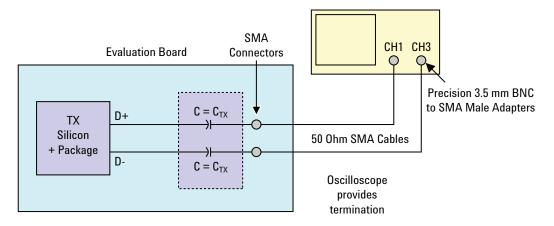

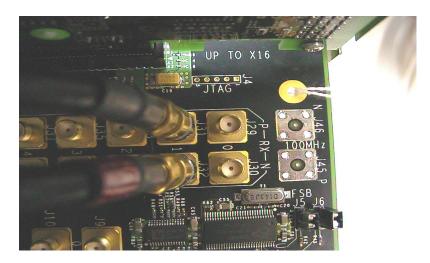

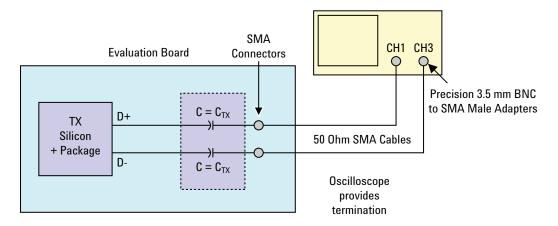

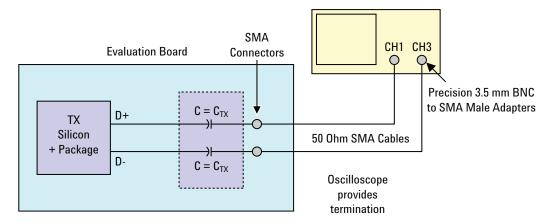

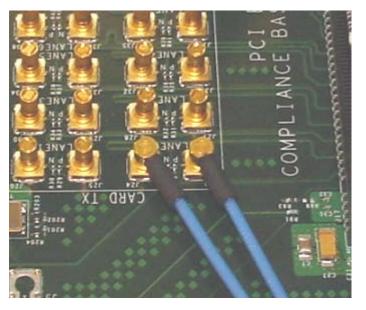

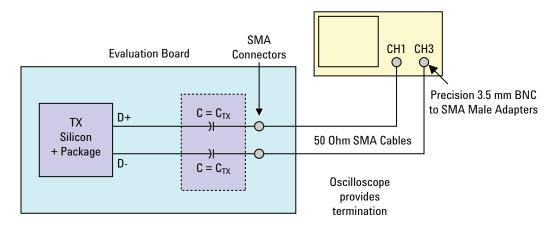

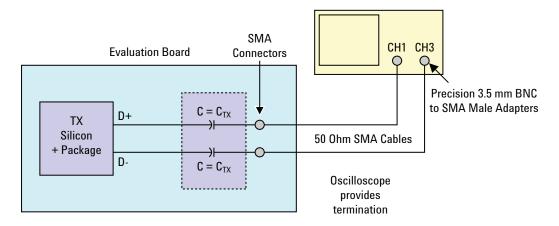

# Single-Ended SMA Probing (Ch1) and (Ch3)

The differential signal is created by the PCI Express Automated Test Application software from the math waveform Ch1-Ch3. The Common mode measurements are also available in this configuration from the common mode waveform (Ch1+Ch3)/2.

This probing technique requires breaking the link and terminating into the 50 ohm/side termination into the oscilloscope. While in this mode, the PCI Express SerDes will transmit the 640 bit Jitter test pattern designed to maximize data dependent jitter.

Channel-to-Channel deskew is required using this technique because two channels are used.

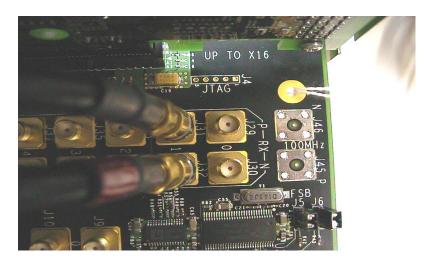

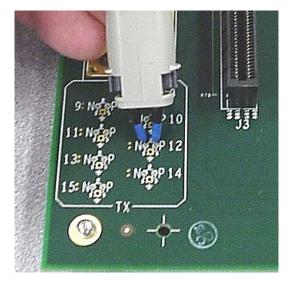

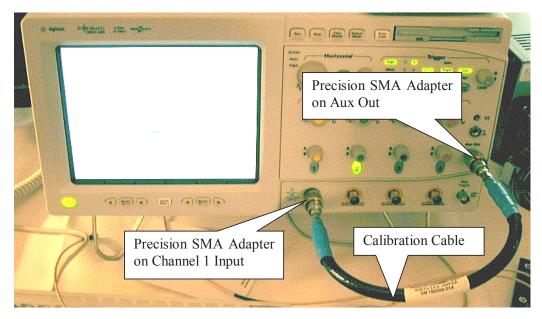

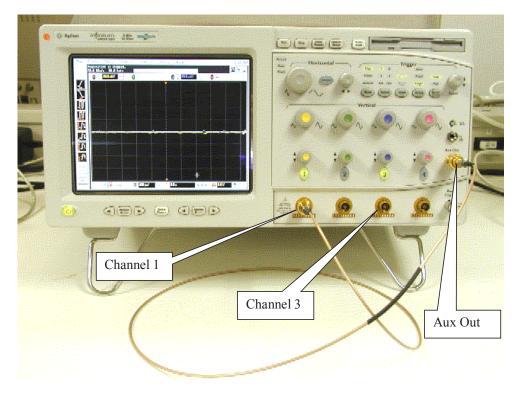

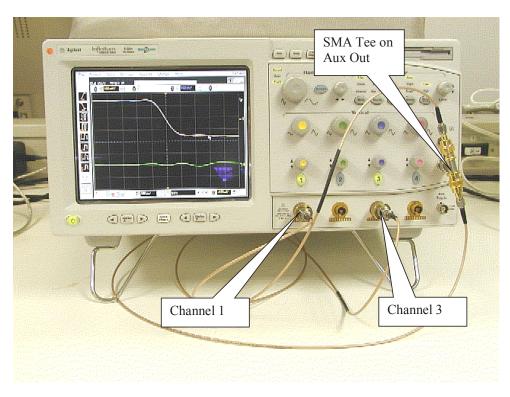

Figure 2 Single-Ended SMA Probing

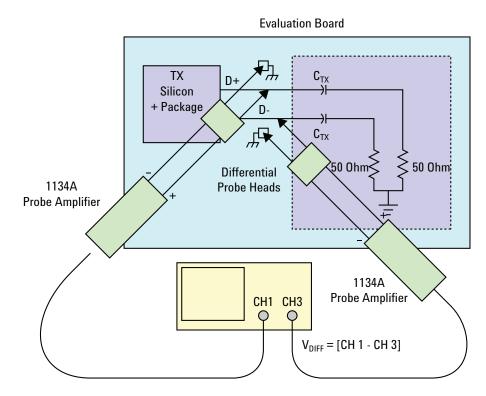

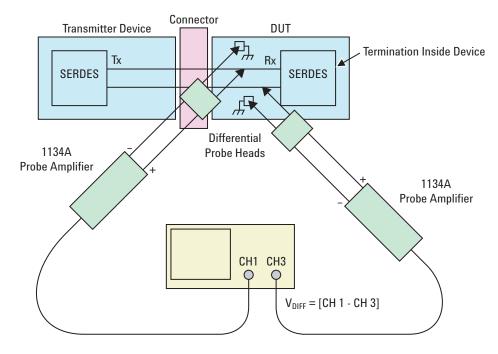

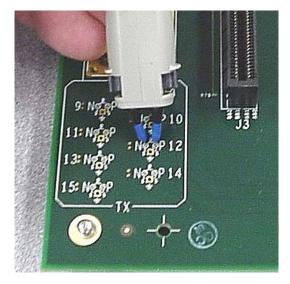

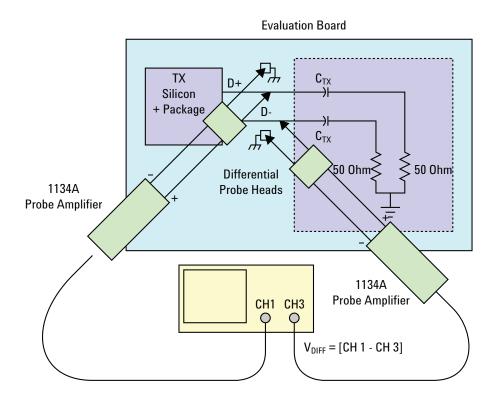

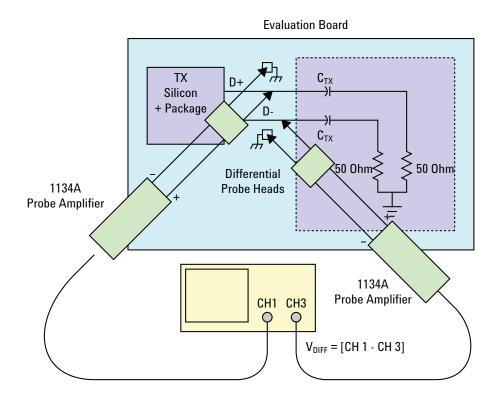

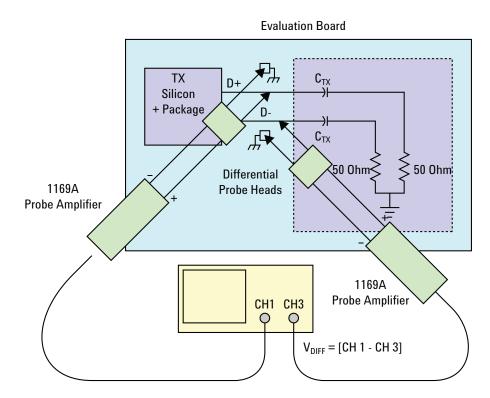

# Single-Ended Probing (Ch1) and (Ch3)

The differential signal is created by the PCI Express Automated Test Application software from the math waveform Ch1-Ch3. The Common mode measurements are also available in this configuration from the common mode waveform (Ch1+Ch3)/2.

Make sure to probe equal distances from the transmitter, as close as possible to the transmitter.

This probing technique requires breaking the link and terminating into 50 ohm/side. While in this mode, the PCI Express SerDes will transmit the 640 bit Jitter test pattern designed to maximize data dependent jitter.

Channel-to-Channel deskew is required using this technique because two channels are used.

For more information on the 1134A probe amplifier and differential probe heads, see Appendix B, "InfiniiMax Probing Options," starting on page 492.

Place single-ended grounds as close to the signal line's reference ground as possible.

Figure 3 Single-Ended Probing

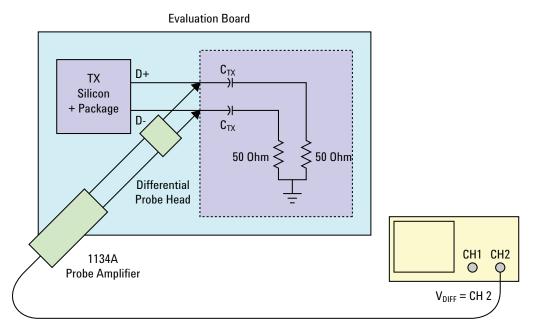

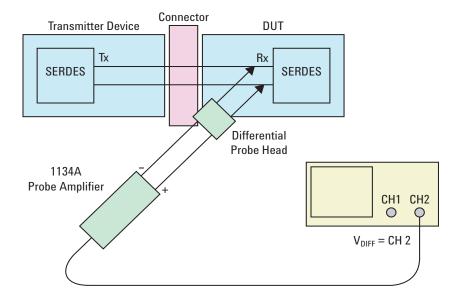

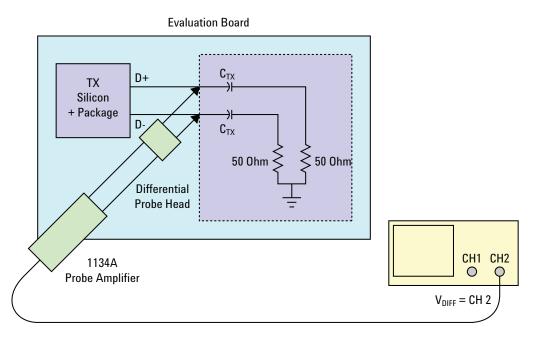

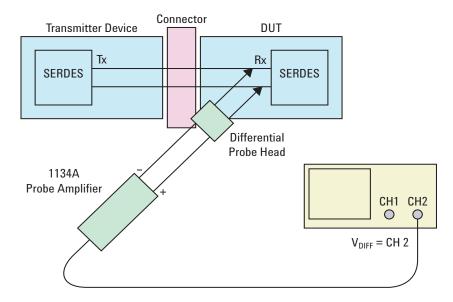

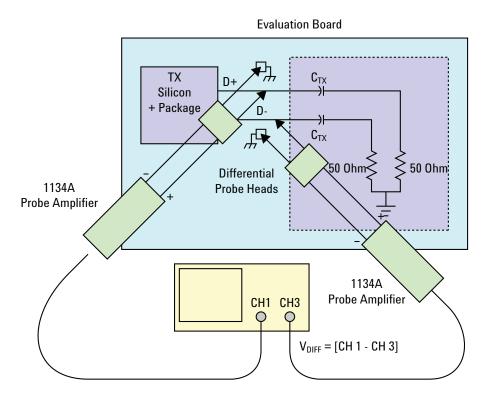

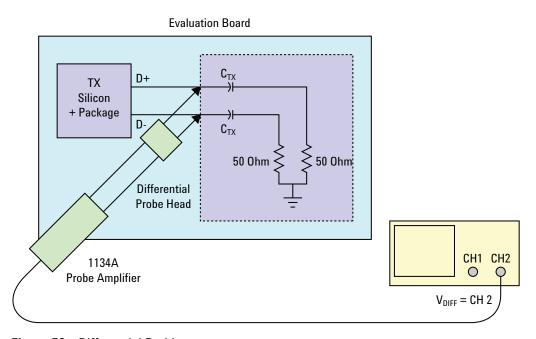

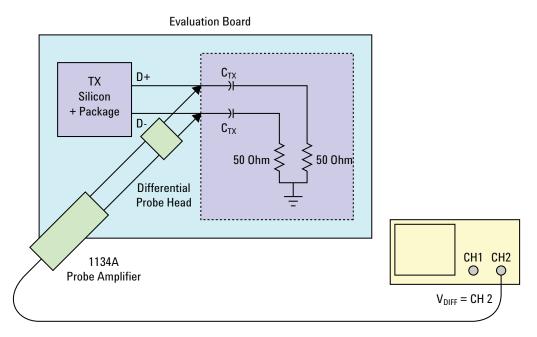

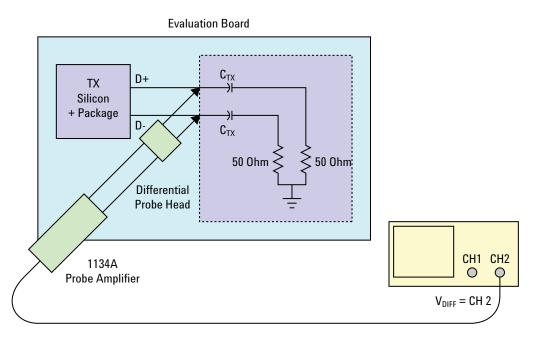

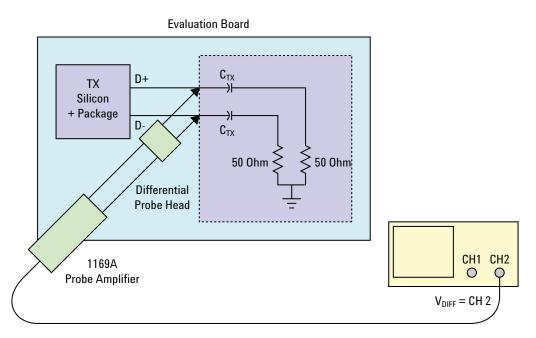

# **Differential Probing (Ch2)**

The differential signal is measured directly by the differential probe head.

Make sure to probe equal distances from the transmitter, as close as possible to the transmitter.

This probing technique requires breaking the link and terminating into 50 ohm/side. While in this mode, the PCI Express SerDes will transmit the 640 bit Jitter test pattern designed to maximize data dependent jitter.

Only one channel of the oscilloscope is used.

For more information on the 1134A probe amplifier and differential probe heads, see Appendix B, "InfiniiMax Probing Options," starting on page 492.

Figure 4 Differential Probing

#### **3** Transmitter (Tx) Tests, PCI-E 1.0a, Full Power

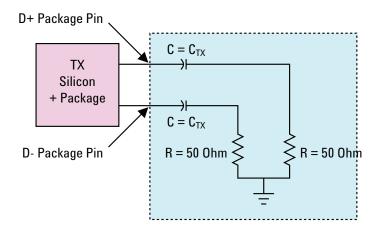

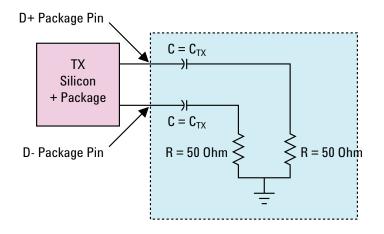

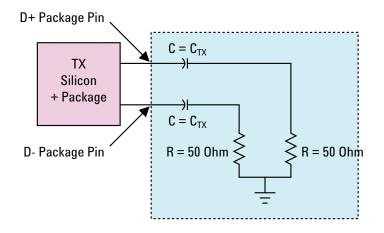

# **Tx Compliance Test Load**

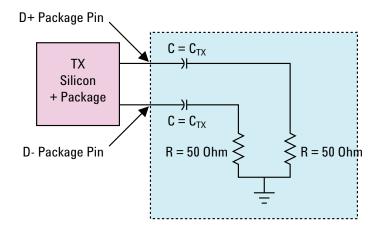

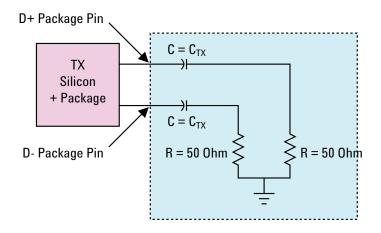

The compliance test load for driver compliance is shown in Figure 4-25 (Base Specification)

Figure 5 Driver Compliance Test Load.

# **Running Signal Quality Tests**

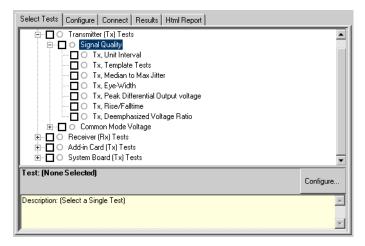

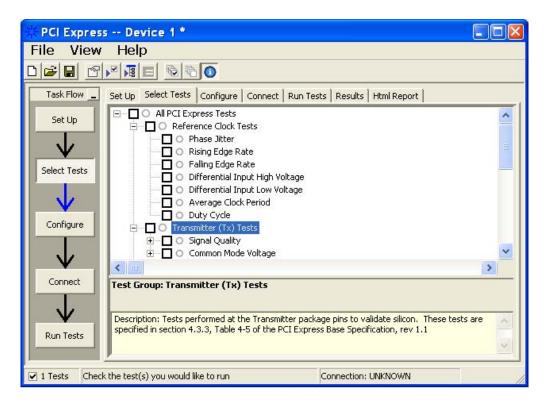

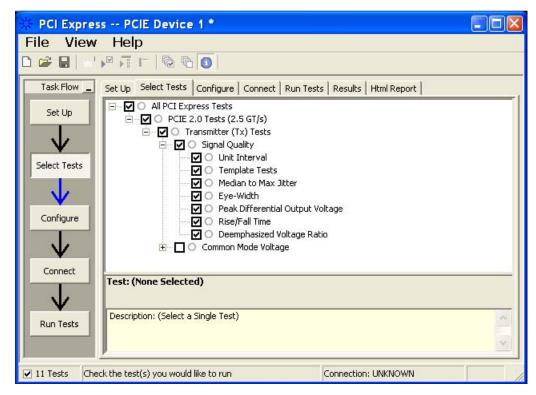

Start the automated testing application as described in "Starting the PCI Express Automated Test Application" on page 24. Then, when selecting tests, navigate to "Signal Quality" in the "Transmitter (Tx) Tests" group.

# **Tx, Unit Interval**

**Table 2**UI from Table 4-5 of the Base Specification.

| Symbol | Parameter     | Min       | Nom   | Max       |

|--------|---------------|-----------|-------|-----------|

| UI     | Unit Interval | 399.88 ps | 400ps | 400.12 ps |

### **Test Definition Notes from the Specification**

- UI (Unit Interval) is specified to be +/-300 ppm.

- UI does not account for SSC dictated variations.

- UI is defined in Table 4-5 (Base Specification).

- UI Characteristics are Maximum UI =400.12 ps and Minimum UI = 399.88ps.

### **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Unit Interval".

### **PASS Condition**

399.88ps < UI < 400.12ps

### **Measurement Algorithm**

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data as the mean unit interval over the clock recovery window.

TX UI(p) = Mean(UI(n))

Where:

n is the index of UI in the current 3500 UI clock recovery window.

p indicates the p<sup>th</sup> 3500 UI clock recovery window advanced from the beginning of the data by p\*100 UI, as described below.

NOTE

The TX UI is computed over 3500 UI. The clock recovery window is then advanced by 100 UI, and another TX UI is computed. This process repeats until the clock recovery window advances beyond the end of the data record. The worst case TX UI is reported.

| Test Name     | Reference                                           | PCI-SIG<br>Assertions |  |  |  |

|---------------|-----------------------------------------------------|-----------------------|--|--|--|

| Unit Interval | PCI Express Base Specification, Rev 1.0a, Table 4-5 | PHY.3.3#2             |  |  |  |

Table 3

Unit Interval Test References

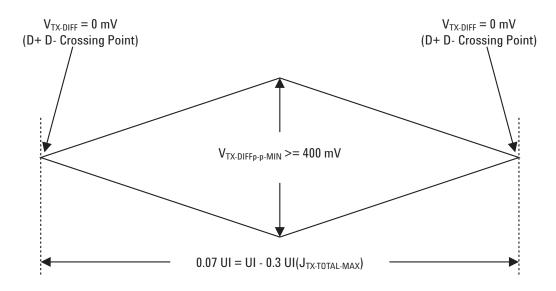

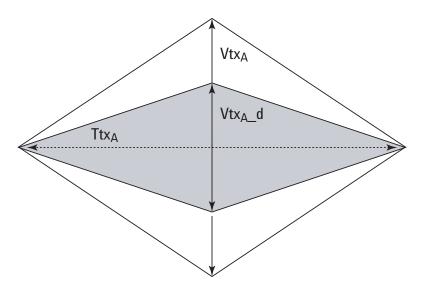

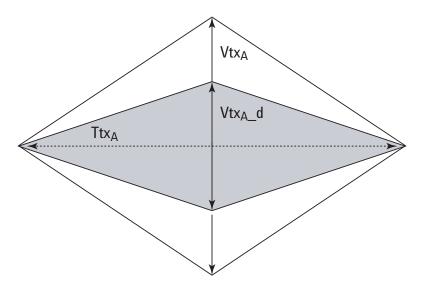

## Tx, Template Tests

See Section 4.3.3.1 of the Base Specification for additional notes and test definitions.

### **Test Definition Notes from the Specification**

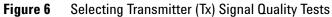

- The TX eye diagram in Figure 4-24 (Base Specification) is specified using the passive compliance/test measurement load in place of any real PCI Express interconnect + RX component.

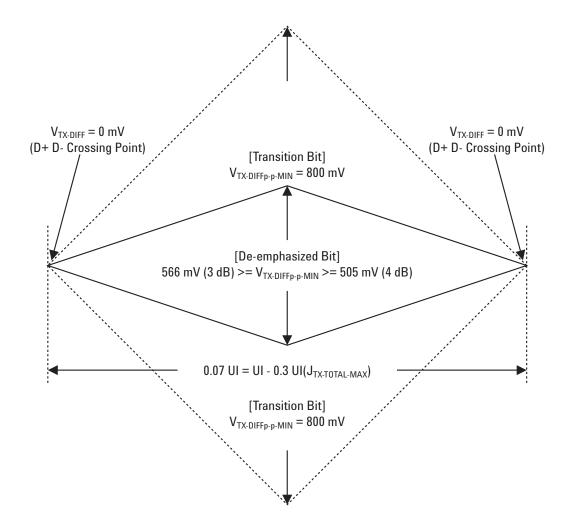

- There are two eye diagrams that must be met for the Transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams will differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit will always be relative to the transition bit.

- The eye diagram must be valid for any 250 consecutive UIs.

- A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### Table 4 Template Tests Test References

| Test Name      | Reference                                                                 | PCI-SIG<br>Assertions |

|----------------|---------------------------------------------------------------------------|-----------------------|

| Template Tests | PCI Express Base Specification, Rev 1.0a,<br>Section 4.3.3.1, Figure 4-26 | PHY.3.3#1             |

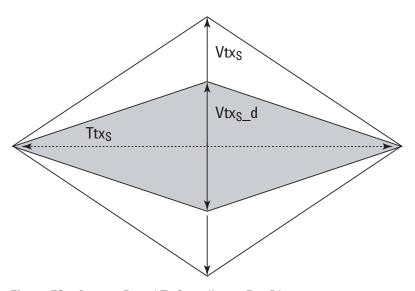

## Tx, Median to Max Jitter

Table 5

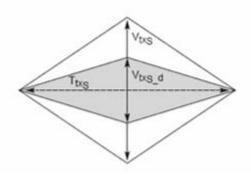

T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> from Table 4-5 of the Base Specification.

| Symbol                                    | Parameter                                                                     | Min | Nom | Max     |

|-------------------------------------------|-------------------------------------------------------------------------------|-----|-----|---------|

| T <sub>TX-EYE</sub> -MEDIAN-to-MAX-JITTER | Maximum time between the jitter median and maximum deviation from the median. |     |     | 0.15 UI |

## **Test Definition Notes from the Specification**

- Jitter is defined as the measurement variation of the crossing points  $(V_{TX-DIFFp-p} = 0 V)$  in relation to the recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used to calculate the TX UI.

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

- A  $T_{TX-EYE}$  = 0.70 UI provides for a total sum of deterministic and random jitter budget of  $T_{TX-JITTER-MAX}$  = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The

$T_{TX\text{-}EYE\text{-}MEDIAN\text{-}to\text{-}MAX\text{-}JITTER}$  specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs.

It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

•  $T_{TX-EYE-MEDIAN-to-MAX-JITTER}$  (Maximum time between the jitter median and maximum deviation from the median.) is defined in Table 4-5 (Base Specification).

### Limits

Maximum = 0.15 UI

### **Pass Condition**

0.15 UI >  $T_{TX-EYE-MEDIAN-to-MAX-JITTER}$

## **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Median to Max Jitter".

### **Measurement Algorithm**

This measurement is made over 250 consecutive bits defined in Section 3.4 (Base Specification).

The measured time difference between a data edge and a recovered clock edge.

$tie(n) = t_{R-DAT}(n) - t_{DAT}(n)$

Where:

t<sub>DAT</sub> is the original data edge.

$t_{R-DAT}$  is the recovered data edge (the ideal time of the data edge as defined by the recovered clock around  $t_{DAT}$ ).

n is the index of all edges in the waveform.

### **Test References**

Table 6

Median to Max Jitter Test References

| Test Name            | Reference                                           | PCI-SIG<br>Assertions |

|----------------------|-----------------------------------------------------|-----------------------|

| Median to Max Jitter | PCI Express Base Specification, Rev 1.0a, Table 4-5 | PHY.3.3#4             |

# Tx, Eye-Width

| Table 7TTABLE 7T | Table 4-5 of the | Base Specification. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|

| Symbol              | Parameter            | Min     | Nom | Max |

|---------------------|----------------------|---------|-----|-----|

| T <sub>TX-EYE</sub> | Minimum TX Eye Width | 0.70 UI |     |     |

## **Test Definition Notes from the Specification**

• The maximum Transmitter jitter can be derived as  $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$  UI.

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

- A  $T_{TX-EYE} = 0.70$  UI provides for a total sum of deterministic and random jitter budget of  $T_{TX-JITTER-MAX} = 0.30$  UI for the Transmitter collected over any 250 consecutive TX UIs. The  $T_{TX-EYE-MEDIAN-to-MAX-JITTER}$  specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs.

## NOTE

The median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

-  $T_{TX-EYE}$  (Minimum TX Eye Width) is defined in Table 4-5 (Base Specification).

### Limits

Minimum = 0.70 UI and the Pass Condition is 0.70 UI <  $T_{TX-EYE}$ .

### **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Eye-Width".

### **Measurement Algorithm**

This measurement is made over 250 consecutive bits defined in Section 3.4 (Base Specification).

The measured minimum horizontal eye opening at the zero reference level as shown in the eye diagram.

$T_{EYE-WIDTH} = UI_{AVG} - TIE_{Pk-Pk}$

Where:

UI<sub>AVG</sub> is the average UI.

$TIE_{Pk-Pk}$  is the Peak-Peak TIE.

### Table 8 Eye-Width Test References

| Test Name Reference |                                                        | PCI-SIG<br>Assertions |  |

|---------------------|--------------------------------------------------------|-----------------------|--|

| Eye-Width           | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.3#9             |  |

## Tx, Peak Differential Output Voltage

| Table 9 | V <sub>TX-DIFFp-p</sub> fi | om Table | 4-5 of the | Base S | pecification. |

|---------|----------------------------|----------|------------|--------|---------------|

|---------|----------------------------|----------|------------|--------|---------------|

| Symbol                  | Parameter                         | Min    | Nom | Max   |

|-------------------------|-----------------------------------|--------|-----|-------|

| V <sub>TX-DIFFp-p</sub> | Differential Pk-Pk Output Voltage | 0.80 V |     | 1.2 V |

## **Test Definition Notes from the Specification**

- $V_{TX-DIFFp-p} = 2^* |V_{TX-D+} V_{TX-D-}|$

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

## **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Peak Differential Output Voltage".

## **PASS Condition**

$0.8 \text{ V} \le V_{\text{TX-DIFF-p-p}} \le 1.2 \text{V}$

### **Measurement Algorithm**

The Differential Peak Voltage measurement returns two times the larger of the Min or Max statistic of the differential voltage waveform.

$V_{TX-DIFF-p-p} = 2^*Max(Max(V_{DIFF(i)}), Min(V_{DIFF(i)}))$

Where:

i is the index of all waveform values.

V<sub>DIFF</sub> is the Differential Voltage signal.

### Table 10 Peak Differential Output Voltage Test References

| Test Name                        | Reference                                              | PCI-SIG<br>Assertions |

|----------------------------------|--------------------------------------------------------|-----------------------|

| Peak Differential Output Voltage | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.2#2             |

## Tx, Rise/Fall Time

Table 11

T<sub>TX-RISE</sub>, T<sub>TX-FALL</sub> from Table 4-5 of the Base Specification.

| Symbol                                      | Parameter                      | Min     | Nom | Max |

|---------------------------------------------|--------------------------------|---------|-----|-----|

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub> | D+/D- TX Output Rise/Fall Time | 0.125UI |     |     |

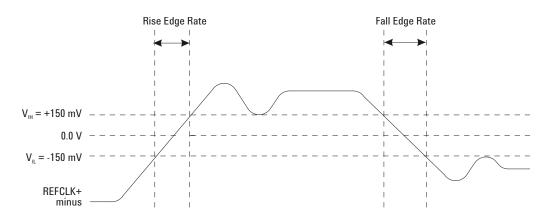

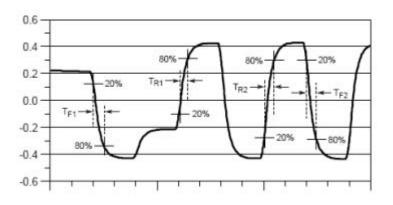

### **Test Definition Notes from the Specification**

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance (Base Specification).

- Measured between 20-80% at Transmitter package pins into a test load as shown in Figure 4-25 for both  $V_{TX\text{-}D\text{+}}$  and  $V_{TX\text{-}D\text{-}}.$

- T<sub>TX-RISE</sub>, T<sub>TX-FALL</sub> (D+/D- TX Output Rise/Fall Time) is defined in Table 4-5 (Base Specification).

### Limits

Minimum = 0.125 UI and the Pass Condition is 0.125 UI <  $T_{TX\text{-}RISE},$   $T_{TX\text{-}FALL}.$

### **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Rise/Fall Time".

### **Measurement Algorithms**

Rise/Fall time is limited to only rising or falling edges of consecutive transitions for transmitter measurements. Rise/Fall Time is taken independently on each single ended waveform sources when you use two single ended probes or two SMA cables as the signal source. Differential signal Rise/Fall Time show up when you select Differential probe type.

**Rise Time.** The Rise Time measurement is the time difference between when the VREF-HI reference level is crossed and the VREF-LO reference level is crossed on the rising edge of the waveform.

$t_{RISE}(n) = t_{HI+}(i) - t_{LO+}(j)$

Where:

t<sub>RISE</sub> is a Rise Time measurement.

$t_{HI+}$  is a set of  $t_{HI}$  for rising edges only.

$t_{\rm LO^+}$  is a set of  $t_{\rm LO}$  for rising edges only.

i and j are indexes for nearest adjacent pairs of  $t_{\rm LO^+}$  and  $t_{\rm HI^+}$

n is the index of rising edges in the waveform.

Rise Time for  $v_{D+}(t)$  is as follows:

$t_{D+RISE}(n) = t_{D+HI+}(i) - t_{D+LO+}(j)$

and for  $v_{D-}(t)$ :

$t_{D-FALL}(n) = t_{D-LO-}(i) - t_{D-HI-}(j)$

**Fall Time.** The Fall Time measurement is the time difference between when the VREF-HI reference level is crossed and the VREF-LO reference level is crossed on the falling edge of the waveform.

$t_{FALL}(n) = t_{LO-}(i) - t_{HI-}(j)$

Where:

t<sub>FALL</sub> is a Fall Time measurement.

$t_{\rm HI-}$  is set of  $t_{\rm HI}$  for falling edge only.

$t_{LO-}$  is set of  $t_{LO}$  for falling edge only.

i and j are indexes for nearest adjacent pairs of  $t_{LO-}$  and  $t_{HI-}$ .

n is the index of falling edges in the waveform.

Fall Time for  $v_{D+}(t)$  is as follows:

$t_{D+FALL}(n) = t_{D+LO-}(i) - t_{D+HI-}(j)$

and for  $v_{D-}(t)$ :

$t_{D-FALL}(n) = t_{D-LO-}(i) - t_{D-HI-}(j)$

### Table 12 Rise/Falltime Test References

| Test Name     | Reference                                              | PCI-SIG<br>Assertions |

|---------------|--------------------------------------------------------|-----------------------|

| Rise/Falltime | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.3#3             |

## Tx, Deemphasized Voltage Ratio

| Symbol                   | Parameter                                            | Min     | Nom     | Max     |

|--------------------------|------------------------------------------------------|---------|---------|---------|

| V <sub>TX-DE-RATIO</sub> | De-Emphasized Differential<br>Output Voltage (Ratio) | -3.0 dB | -3.5 dB | -4.0 dB |

Table 13

V<sub>TX-DF-BATIO</sub> from Table 4-5 of the Base Specification.

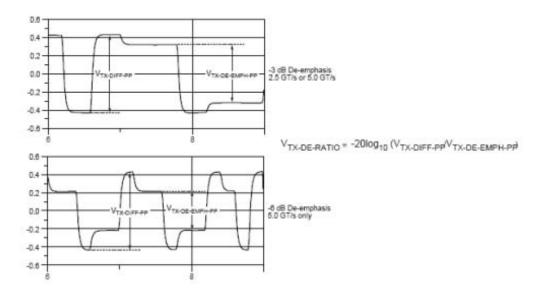

### **Test Definition Notes from the Specification**

- This is the ratio of the  $V_{TX\text{-}DIFFp\text{-}p}$  of the second and following bits after a transition divided by the  $V_{TX\text{-}DIFFp\text{-}p}$  of the first bit after a transition.

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) in the serial data standard and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

- $V_{TX-DE-RATIO}$  (De-Emphasized Differential Output Voltage (Ratio)) is defined in Table 4-5 (Base Specification).

## Limits

Minimum = -4.0 dB and Maximum = -3.0 dB, and the Pass Condition is -4.0 dB <  $V_{TX\text{-}DE\text{-}RATIO}$  < -3.0 dB.

### **Test Procedure**

Follow the procedure in "Running Signal Quality Tests" on page 36, and select "Deemphasized Voltage Ratio".

### **Measurement Algorithm**

This measurement is made over 250 consecutive bits defined in Section 3.4 (Base Specification).

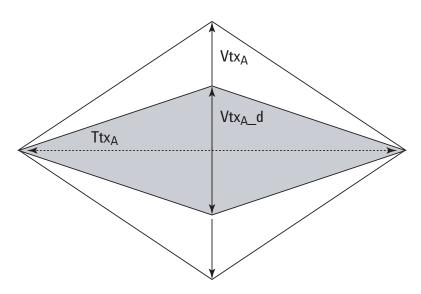

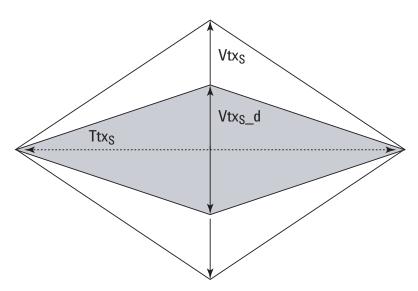

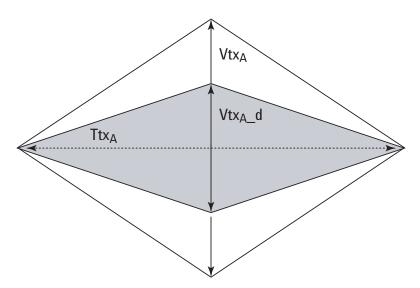

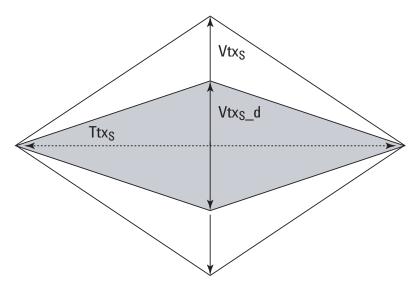

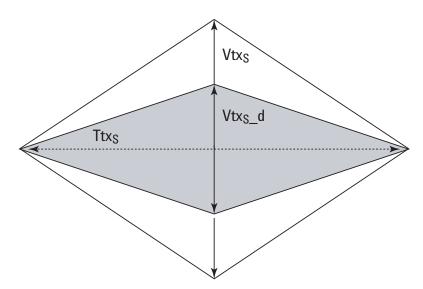

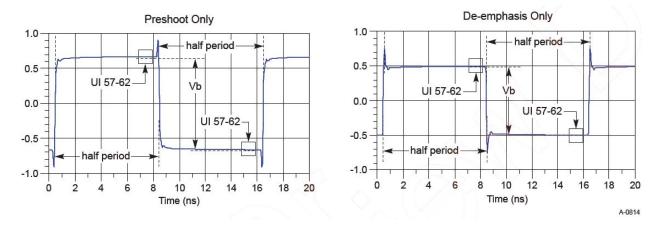

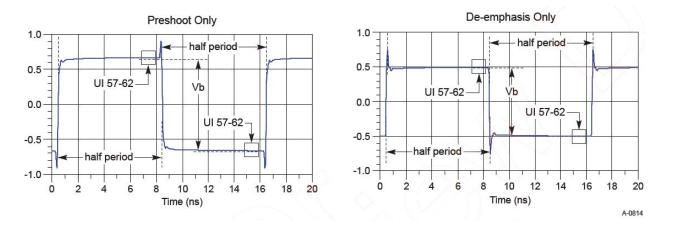

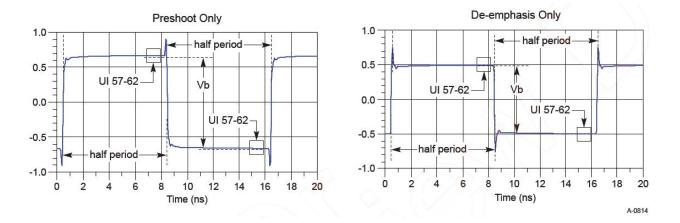

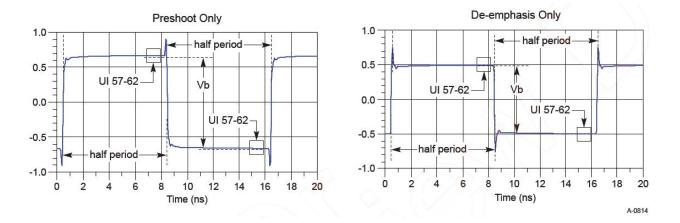

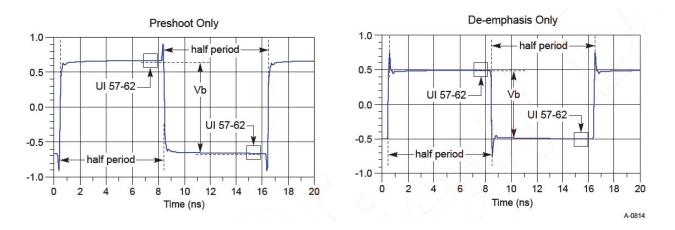

The De-Emphasis measurement calculates the ratio of any non-transition eye voltage (2nd, 3rd, etc. eye voltage succeeding an edge) to its nearest preceding transition eye voltage (1st eye voltage succeeding an edge). In Figure 7, it is the ratio of the black voltages over the blue voltages. The results are given in dB.

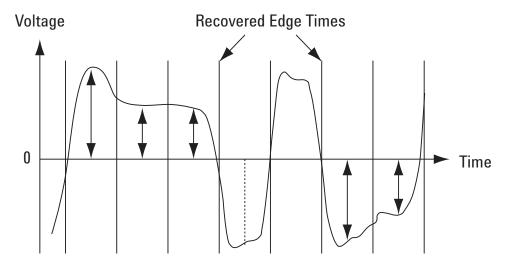

Figure 8 DeEmphasis Measurement.

DEEM(m) =

$$dB\left(\frac{v_{\text{EYE-HI-NTRAN}}(m)}{v_{\text{EYE-HI-TRAN}}(n)}\right)$$

or

$$DEEM(m) = dB\left(\frac{v_{EYE-LO-NTRAN}(m)}{v_{EYE-LO-TRAN}(n)}\right)$$

Where:

$v_{\mbox{\scriptsize EYE-HI-TRAN}}$  is the High voltage at mid UI following a positive transition.

$v_{\mbox{EYE-LO-TRAN}}$  is the Low voltage at mid UI following a negative transition.

$v_{\mbox{\scriptsize EYE-HI-NTRAN}}$  is the High voltage at mid UI following a positive transition bit.

$v_{\mbox{EYE-LO-NTRAN}}$  is the Low voltage at mid UI following a negative transition bit.

m is the index for all non-transition UIs.

n is the index for the nearest transition UI preceding the UI specified by m.

## **Test References**

| Test Name                  | Reference                                              | PCI-SIG<br>Assertions |

|----------------------------|--------------------------------------------------------|-----------------------|

| Deemphasized Voltage Ratio | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.2#1             |

# **Running Common Mode Voltage Tests**

Start the automated testing application as described in "Starting the PCI Express Automated Test Application" on page 24. Then, when selecting tests, navigate to "Common Mode Voltage" in the "Transmitter (Tx) Tests" group.

| Select Tests Configure Connect Results Html Report                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All PCI Express Tests     Transmitter (Tx) Tests     Signal Quality     Common Mode Voltage     Tx, RMS AC Peak Common Mode Output Voltage     Tx, Avg DC Common Mode Output Voltage     Tx, DC Common Mode Output Voltage     Addrin Card (Tx) Tests     System Board (Tx) Tests |

| Test: (None Selected) Configure                                                                                                                                                                                                                                                                                                                                                                     |

| Description: (Select a Single Test)                                                                                                                                                                                                                                                                                                                                                                 |

# Tx, RMS AC Peak Common Mode Output Voltage

| Symbol                 | Parameter                                 | Min | Nom | Max   |

|------------------------|-------------------------------------------|-----|-----|-------|

| V <sub>TX-CM-ACp</sub> | RMS AC Peak Common Mode<br>Output Voltage |     |     | 20 mV |

**Table 15**VTX-CM-ACp from Table 4-5 of the Base Specification.

### **Test Definition Notes from the Specification**

```

V_{\text{TX-CM-ACp}} = \text{RMS}(|V_{\text{TX-D+}} + V_{\text{TX-D-}}| \div 2 - V_{\text{TX-CM-DC}})V_{\text{TX-CM-DC}}

= DC<sub>(avg)</sub> of |V<sub>TX-D+</sub> + V<sub>TX-D-</sub>| ÷ 2

```

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

- V<sub>TX-CM-ACp</sub> (RMS AC Pk Common Mode Output Voltage) is defined in Table 4-5 (Base Specification).

### Limits

Maximum = 20 mV and the Pass Condition is 20 mV >  $V_{TX-CM-ACD}$ .

### **Test Procedure**

Follow the procedure in "Running Common Mode Voltage Tests" on page 48, and select "RMS AC Peak Common Mode Output Voltage".

NOTE

This test is only available when the single-ended or SMA probing method has been used (see "Probing the Link for Tx Compliance" on page 32).

### **Measurement Algorithm**

**AC CM RMS Voltage**. The AC Common Mode RMS Voltage measurement calculates the RMS statistic of the Common Mode voltage waveform with the DC Value removed.

$v_{AC-RMS-CM}(i) = RMS(v_{AC-M}(i))$

Where:

i is the index of all waveform values.

$v_{AC\text{-}RMS\text{-}CM}$  is the RMS of the AC Common Mode voltage signal.

$v_{AC-M}$  is the AC Common Mode voltage signal.

### Table 16 RMS AC Peak Common Mode Output Voltage Test References

| Test Name                                 | Reference                                              | PCI-SIG<br>Assertions |

|-------------------------------------------|--------------------------------------------------------|-----------------------|

| RMS AC Peak Common Mode<br>Output Voltage | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.3#5             |

## Tx, Avg DC Common Mode Output Voltage

| Table 17 | V <sub>TX-DC-CM</sub> from | Table 4-5 of the | Base Specification. |

|----------|----------------------------|------------------|---------------------|

|----------|----------------------------|------------------|---------------------|

| Symbol                | Parameter                        | Min | Nom | Max   |

|-----------------------|----------------------------------|-----|-----|-------|

| V <sub>TX-DC-CM</sub> | The TX DC Common Mode<br>Voltage | 0 V |     | 3.6 V |

### **Test Definition Notes from the Specification**

The TX DC common mode voltage ( $V_{TX-DC-CM}$ ) must be held at the same value during all states. The allowable range for  $V_{TX-DC-CM}$  is 0 to 3.6 V (+/- 100mV).

## Limits

0 V <=  $V_{TX-DC-CM}$  <= 3.6 V

### **Test Procedure**

Follow the procedure in "Running Common Mode Voltage Tests" on page 48, and select "Avg DC Common Mode Output Voltage".

## NOTE

This test is only available when the single-ended or SMA probing method has been used (see "Probing the Link for Tx Compliance" on page 32).

### **Measurement Algorithm**

The Avg DC Common Mode Voltage measurement computes the DC average of the common mode signal:

$V_{TX-DC-CM} = DC_{(avg)}$  of  $|V_{TX-D+} + V_{TX-D-}|/2$

NOTE

The base specification states that  $V_{TX-DC-CM}$  must be held at the same value during all states. For complete validation, this measurement should be performed on the device in all states and the results compared.

### Table 18 Avg DC Common Mode Output Voltage Test References

| Test Name                            | Reference                                              | PCI-SIG<br>Assertions |

|--------------------------------------|--------------------------------------------------------|-----------------------|

| Avg DC Common Mode Output<br>Voltage | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.1#12            |

## Tx, DC Common Mode Line Delta

| Table 19 | VTX-CM-DC-LINF-DFLTA | from | Table 4-5 of the Bas | se Specification |

|----------|----------------------|------|----------------------|------------------|

|          |                      |      |                      |                  |

| Symbol                           | Parameter                                                        | Min | Nom | Max   |

|----------------------------------|------------------------------------------------------------------|-----|-----|-------|

| V <sub>TX-CM-DC-LINE-DELTA</sub> | Absolute Delta of DC Common<br>Mode Voltage between D+ and<br>D- | 0 V |     | 25 mV |

## **Test Definition Notes from the Specification**

$\begin{aligned} |V_{TX-CM-DC-D+} - V_{TX-CM-DC-D-}| &\leq 25 \text{ mV}, V_{TX-CM-DC-D+} \\ &= DC_{(avg)} \text{ of } |V_{TX-D+}|, V_{TX-CM-DC-D-} &= DC_{(avg)} \text{ of } |V_{TX-D-}| \end{aligned}$

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 4-25 (Base Specification) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 4-24 (Base Specification).

- $V_{TX-CM-DC-LINE-DELTA}$  (Absolute Delta of DC Common Mode Voltage between D+ and D-) Is defined in Table 4-5 (Base Specification).

### Limits

$V_{TX-CM-LINE-DELTA} < 25 mV$

## **Test Procedure**

Follow the procedure in "Running Common Mode Voltage Tests" on page 48, and select "DC Common Mode Line Delta".

NOTE

This test is only available when the single-ended or SMA probing method has been used (see "Probing the Link for Tx Compliance" on page 32).

### **Measurement Algorithm**

$V_{TX-CM-LINE-DELTA}$  is computed as the absolute value of the difference between the DC average of  $V_{TX-D+}$  and the DC average of  $V_{TX-D-}$

$V_{TX-CM-LINE-DELTA} = |V_{TX-CM-DC+} - V_{TX-CM-DC-D-}|$

Where:

$V_{TX-CM-DC+}$  is the DC<sub>(avg)</sub> of  $V_{TX-D+}$

V<sub>TX-CM-DC-</sub> is the DC<sub>(avg)</sub> of V<sub>TX-D-</sub>

### **Test References**

### Table 20 DC Common Mode Line Delta Test References

| Test Name                 | Reference                                              | PCI-SIG<br>Assertions |

|---------------------------|--------------------------------------------------------|-----------------------|

| DC Common Mode Line Delta | PCI Express Base Specification, Rev 1.0a, Table<br>4-5 | PHY.3.1#26            |

## Tx, DC Common Mode Output Voltage Variation

### **Test Definition Notes from the Specification**

The TX DC common mode voltage ( $V_{TX-DC-CM}$ ) must be held at the same value during all states. The allowable range for  $V_{TX-DC-CM}$  is 0 to 3.6 V (+/- 100mV).

### Limits

$|V_{TX-DC-CM-VARIATION}| \le 100 \text{ mV}$

### **Test Procedure**

Follow the procedure in "Running Common Mode Voltage Tests" on page 48, and select "DC Common Mode Output Voltage Variation".

This test is only available when the single-ended or SMA probing method has been used (see "Probing the Link for Tx Compliance" on page 32).

### **Measurement Algorithm**

The Tx DC Common Mode Output Voltage Variation measurement computes the worst case positive or negative excursion of the common mode signal from the average DC Common Mode Voltage  $V_{TX-DC-CM}$

NOTE

$V_{TX-DC-CM-VARIATION} = | Max( Max(V_{CM(i)}), Min(V_{CM(i)})) - V_{TX-DC-CM} |$

Where:

i is the index of all waveform values.

$V_{CM}$  is the common mode signal (V\_{TX-D+} + V\_{TX-D-})/2.

## **Test References**

| Table 21 | DC Common | Mode Output | Voltage V | /ariation | Test References |

|----------|-----------|-------------|-----------|-----------|-----------------|

|          |           |             |           |           |                 |

| Test Name                                  | Reference                                                            | PCI-SIG<br>Assertions |

|--------------------------------------------|----------------------------------------------------------------------|-----------------------|

| DC Common Mode Output Voltage<br>Variation | PHY ELECTRICAL TEST CONSIDERATIONS,<br>REVISION 1.0RD, Section 4.1.6 | PHY.3.1#12            |

Transmitter (Tx) Tests, PCI-E 1.0a, Full Power

4

Agilent N5393C PCI Express Automated Test Application Compliance Testing Methods of Implementation

# Transmitter (Tx) Tests, PCI-E 1.0a, Low Power

Probing the Link for Tx Compliance 57 Tx Compliance Test Load 57 Running Signal Quality Tests 57 Running Common Mode Voltage Tests 60

This section provides the Methods of Implementation (MOIs) for Transmitter tests using an Agilent 90000X series Infinium oscilloscope, 1134A or 1169A probes, and the PCI Express Automated Test Application.

The Mobile Graphic Low Power Addendum to The PCIE Base Specification 1.0 describes the reduced power requirement of a transmitter on Mobile Platform. To meet low power requirement, a device must be compliant to the PCIE Base Specification 1.0a except for electrical specification in section 2.2 of the addendum. The addendum also states that a low power device does not implement de-emphasis.

PCIE 1.0a Low Power Transmitter Tests consist of all tests from PCIE 1.0 Full (Standard) Power Tests except de-emphasis tests. The following table shows all the PCIE 1.0a Low Power Tests:

| Test Name                               | Remarks            | See      |

|-----------------------------------------|--------------------|----------|

| Unit Interval                           | Same as Full Power | page 37. |

| Template Tests                          | Different          | page 58. |

| Median to Max Jitter                    | Different          | page 59. |

| Eye-Width                               | Different          | page 59. |

| Peak Differential Output Voltage        | Different          | page 59. |

| Rise/Fall Time                          | Same as Full Power | page 44. |

| RMS AC Peak Common Mode Output Voltage  | Same as Full Power | page 48. |

| Avg DC Common Mode Output Voltage       | Same as Full Power | page 50. |

| DC Common Mode Output Voltage Variation | Same as Full Power | page 52. |

| DC Common Mode Line Delta               | Same as Full Power | page 51. |

Table 22

PCIE 1.0a Low Power Transmitter Tests

All the tests above remarked with "Same as Full Power" share the same Method of Implementation (MOI) with PCIE 1.0 Full Power (refer to the page numbers shown). The differences in the test method are described in this chapter.

# **Probing the Link for Tx Compliance**

When performing low-power transmitter tests, probing is the same as for full-power tests. See "Probing the Link for Tx Compliance" on page 32.

# **Tx Compliance Test Load**

When performing low-power transmitter tests, the compliance test load is the same as for full-power tests. See "Tx Compliance Test Load" on page 36.

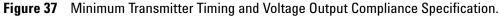

# **Running Signal Quality Tests**

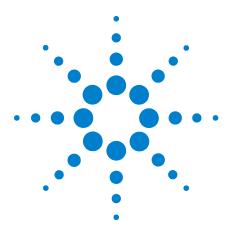

Start the automated testing application as described in "Starting the PCI Express Automated Test Application" on page 24. Then, when selecting tests, navigate to "Signal Quality" in the "Transmitter (Tx) Tests" group.

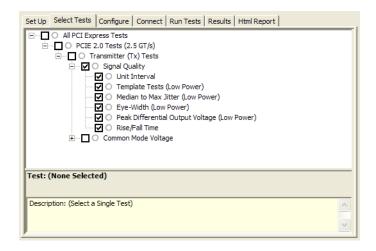

Figure 10 Selecting Transmitter (Tx) Signal Quality Tests

## Tx, Unit Interval

When performing low-power transmitter tests, the Tx Unit Interval test is the same as for full-power tests. See "Tx, Unit Interval" on page 37.

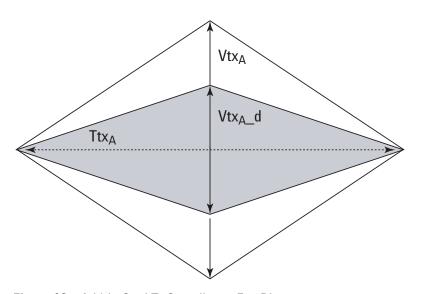

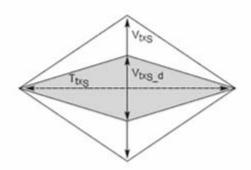

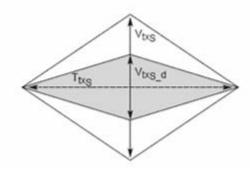

## Tx, Template Tests (Low Power)

### **Test Definition/Reference**

### Mobile Graphics Low-Power Addendum to the PCI Express Base Specification 1.0

- Compliance of the transmitter eye diagram uses the same methodology as outlined in PCI Express Base 1.0a. The Tx eye diagram is specified using the passive compliance/test measurement load (see Figure 2-1 of Mobile Low Power PCIE Specification) in place of any real PCI Express interconnect plus Rx component. Because de-emphasis is not implemented, the transition and de-emphasized bit transitions are merged into a single Transmitter compliance eye diagram.

- The eye diagram must be valid for any 250 consecutive UIs.

- A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

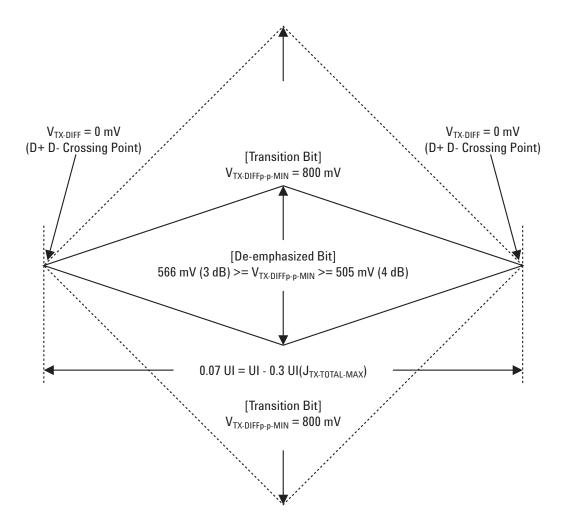

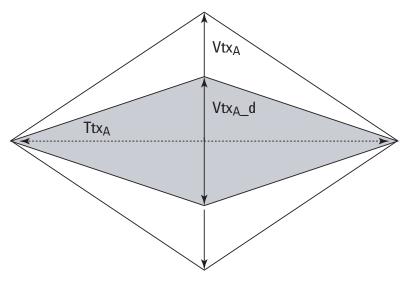

**Figure 11** Transmitter Compliance Eye Diagram from Figure 2-2 of the Mobile Graphic Low-Power Addendum.

### **Difference in Test Procedure Compared to Full Power**

- Different Eye diagram used. The Eye diagram can be found in Figure 2.2 of Mobile Low Power PCIE Specification.

- Eye diagram only runs once with both transition and non-transition bits since de-emphasis is no longer needed for low power specification.

See Also "Tx, Template Tests" on page 38.

## Tx, Median to Max Jitter (Low Power)

### **Difference in Test Procedure Compared to Full Power**

- Eye diagram only runs once with both transition and non-transition bits since de-emphasis is no longer needed for low power specification.

- See Also "Tx, Median to Max Jitter" on page 40.

## Tx, Eye-Width (Low Power)

### **Difference in Test Procedure Compared to Full Power**

- Eye diagram only runs once with both transition and non-transition bits since de-emphasis is no longer needed for low power specification.

- **See Also** "Tx, Eye-Width" on page 41.

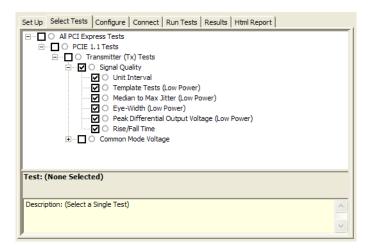

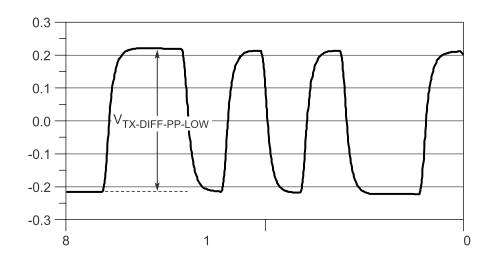

## Tx, Peak Differential Output Voltage (Low Power)

### **Difference in Test Procedure Compared to Full Power**

• Different specification used:

**Table 23** $V_{TX-DIFFp-p}$  from Table 2-1 of the Mobile Graphic Low-Power Addendum.

| Symbol                  | Parameter                         | Min     | Nom | Max   |

|-------------------------|-----------------------------------|---------|-----|-------|

| V <sub>TX-DIFFp-p</sub> | Differential Pk-Pk Output Voltage | 0.400 V |     | 1.2 V |

- $V_{TX-DIFFp-p} = 2^* |V_{TX-D+} V_{TX-D-}|$

- Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 2-1 (Mobile Graphic Low Power Addemdum) and measured over any 250 consecutive TX UIs. Also refer to the Transmitter compliance eye diagram shown in Figure 2-2 (Mobile Graphic Low Power Addemdum).

### See Also "Tx, Peak Differential Output Voltage" on page 43.

## Tx, Rise/Fall Time

When performing low-power transmitter tests, the Tx Rise/Fall Time test is the same as for full-power tests. See "Tx, Rise/Fall Time" on page 44.

# **Running Common Mode Voltage Tests**

When performing low-power transmitter tests, the common mode voltage tests are the same as for full-power tests. See "Running Common Mode Voltage Tests" on page 48.

5

Agilent N5393C PCI Express Automated Test Application Compliance Testing Methods of Implementation

# Receiver (Rx) Tests, PCI-E 1.0a

Probing the Link for Rx Compliance 62 Running Receiver Tests 65

This section provides the Methods of Implementation (MOIs) for Receiver tests using an Agilent 90000X series Infinitum oscilloscope, 1134A or 1169A probes, and the PCI Express Automated Test Application.

## NOTE

None of the included receiver tests validate the receiver's ability to correctly receive data (also known as receiver tolerance). Rather, they validate that the signal as seen by the reciever meets or exceeds various parameters (maximum voltage, jitter, eye width, etc.). These tests validate the transmitter and interconnect. Separate reciever tolerance testing is required to ensure the receiver is correctly receiving data.

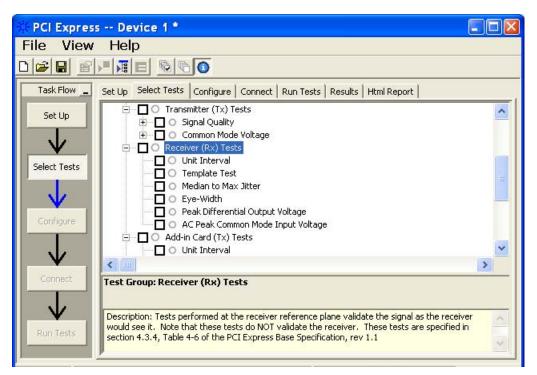

# **Probing the Link for Rx Compliance**

Receiver tests are done by probing the link as close as is feasibly possible to the pins of the receiver device. Alternatively, a dummy load can be used for the termination of the link. To probe the receiver link, you can:

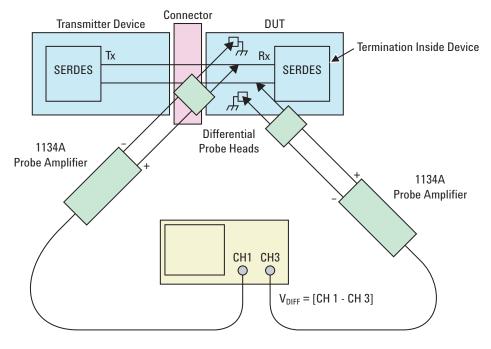

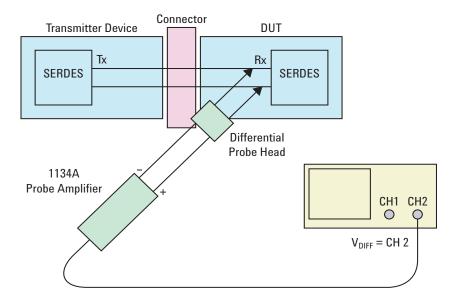

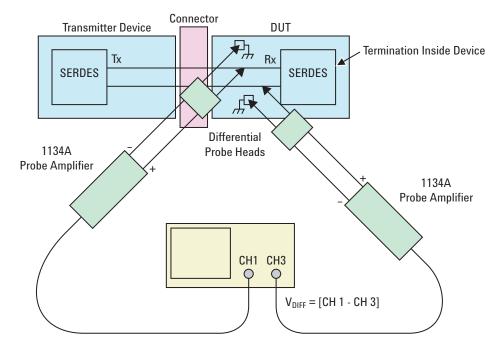

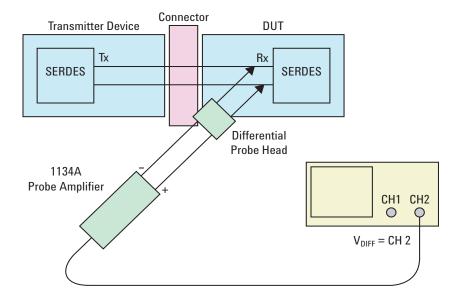

- Use two differential probe heads with two 1134A probe amplifiers (with the negative lead grounded for single-ended measurements) and the Ch1 and Ch3 inputs of an oscilloscope that has 20 GS/s sample rate available on two channels.

- Use one differential probe head with the 1134A probe amplifier and the Ch2 input of an oscilloscope that has 20 GS/s sample rate available on that channel.

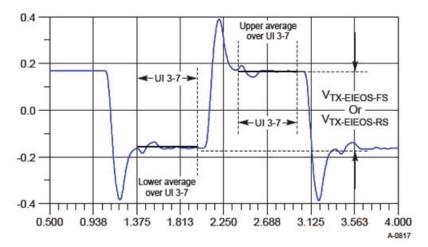

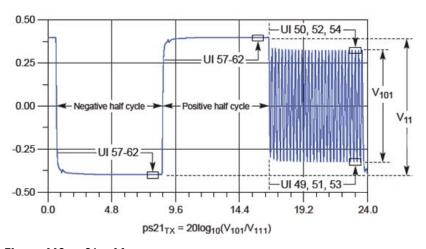

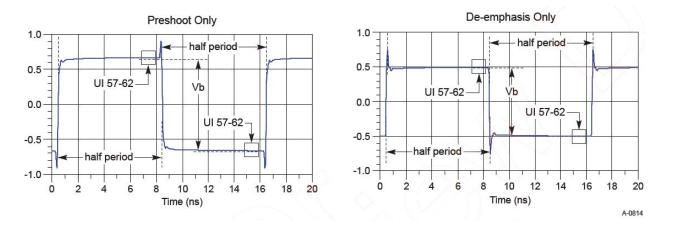

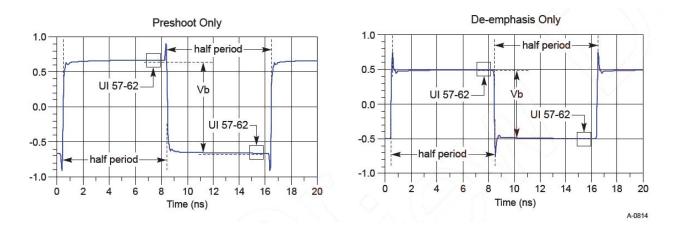

|            | Probing (                                                     | Probing Configurations  |                  |                      | aveforms       |